# $\square$

# TrueMask<sup>®</sup> ILT MWCO: Full-Chip Curvilinear ILT in a Day & Full Mask Multi-Beam and VSB Writing in 12 hours for 193i

FEBRUARY 26, 2020 | <sup>1</sup>LINYONG (LEO) PANG, PHD

P. Jeffrey Ungar, Ali Bouaricha, Lu Sha, Michael Pomerantsev, Mariusz Niewczas, Kechang Wang Bo Su, Ryan Pearman, Aki Fujimura

D2S, Inc. (US)

D2S<sup>®</sup> and TrueMask<sup>®</sup> are US-registered trademarks of D2S, Inc. in US. TrueMask<sup>®</sup> and TrueModel<sup>®</sup> are registered trademarks of D2S, Inc. in US, Japan, Korea, China and Taiwan.

# Full-Chip Curvilinear ILT is Much Faster to Compute and Write with VSB Than You Think

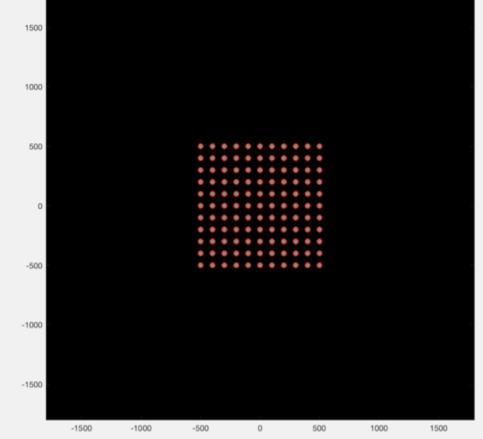

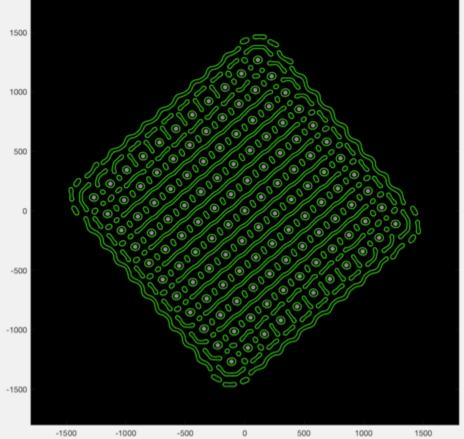

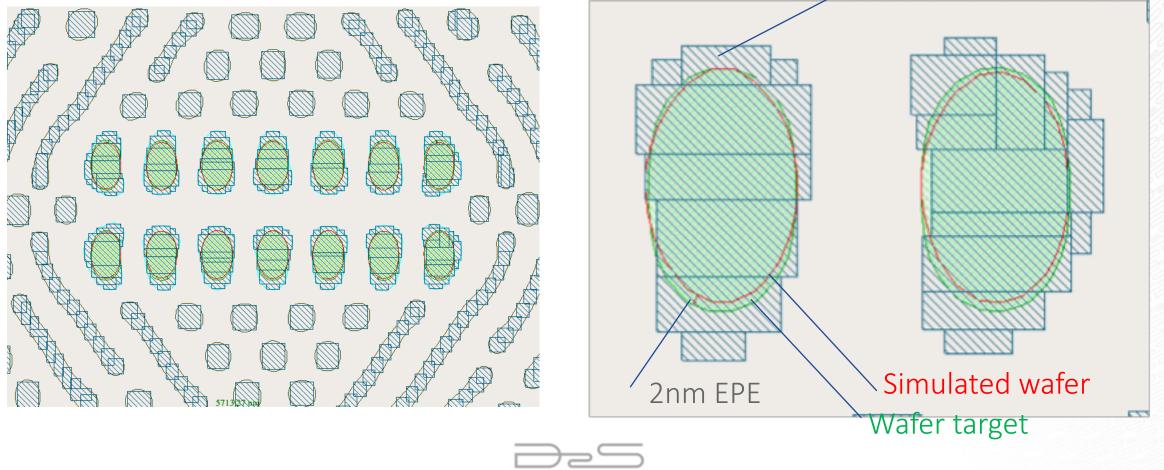

Corresponding wafer target & simulated wafer contours

# ILT with Level-Set Method Started a Decade Ago

#### **Fast Inverse Lithography Technology**

Daniel S. Abrams, Linyong Pang Luminescent Technologies, Inc., 650 Castro Street, Suite 220, Mountain View, CA 94041, U.S.A.

# A Different Approach based on GPU Invented by GAUDA, Extended by D2S

|                |                                                                                                      | US007856612B1                                                                                    |  |  |  |  |

|----------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

|                | (12) United States Patent<br>Ungar et al.                                                            | <ul> <li>(10) Patent No.: US 7,856,612 B1</li> <li>(45) Date of Patent: Dec. 21, 2010</li> </ul> |  |  |  |  |

|                | (54) LITHOGRAPHY MASK DESIGN THROUG<br>MASK FUNCTIONAL OPTIMIZATION AN<br>SPATIAL FREQUENCY ANALYSIS | D 7,063,920 B2* 6/2006 Baba-Ali 430/5<br>7,266,803 B2 9/2007 Chou et al.                         |  |  |  |  |

|                |                                                                                                      |                                                                                                  |  |  |  |  |

| Target Pattern | Continuous Tone<br>Fourier ILT Mask                                                                  | Binary Fourier<br>ILT Mask                                                                       |  |  |  |  |

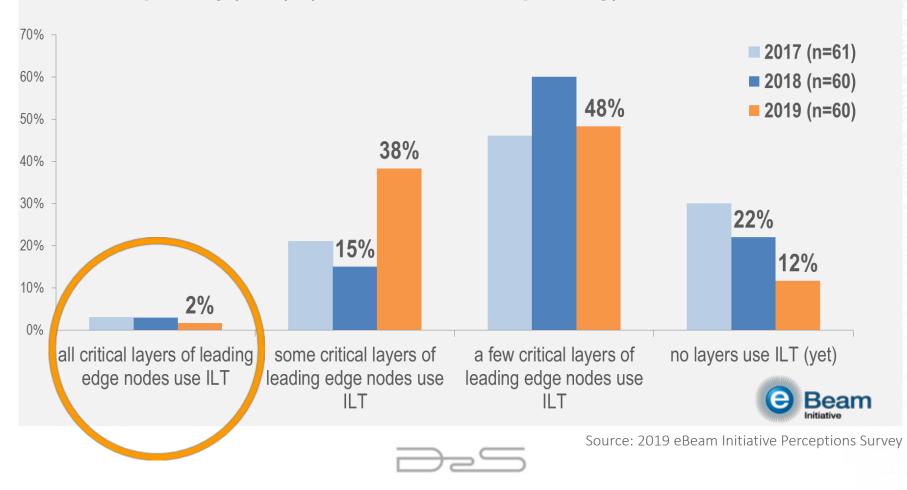

# Why isn't Curvilinear ILT Used in All Critical Layers?

How broadly is inverse lithography technology (ILT) used for production chips today (2019)? (use includes for hot spots only) Select one answer.

### Before: ILT Mask Write Time is Too Long Now: Multi-beam Mask Writers Enable Curvilinear ILT

Conventional VSB mask writer

- Generates too many shots

- Takes too long to write

Multi-beam mask writer

- Designed for curvilinear ILT

- Writes any shape in constant time

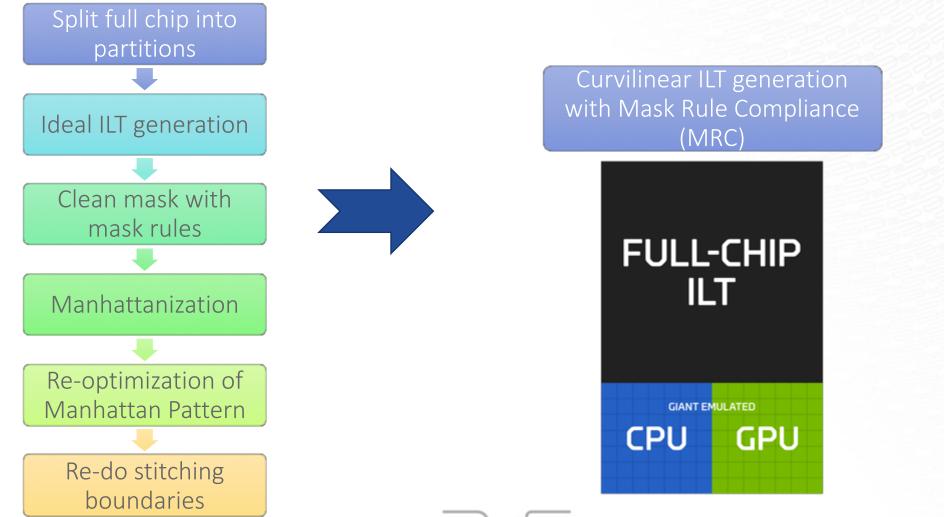

### Before: Full Chip ILT Run Time is too Long Now: TrueMask<sup>®</sup> ILT Solves ILT Computing Challenges

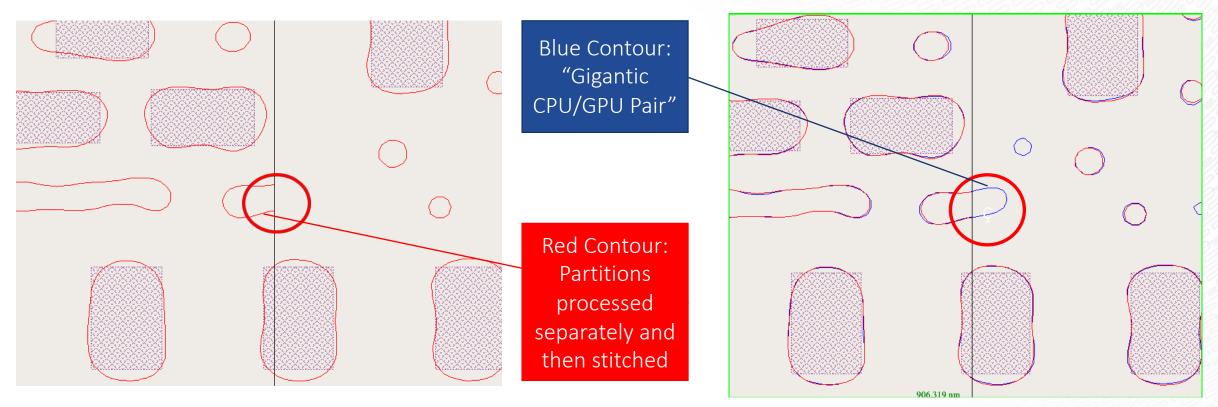

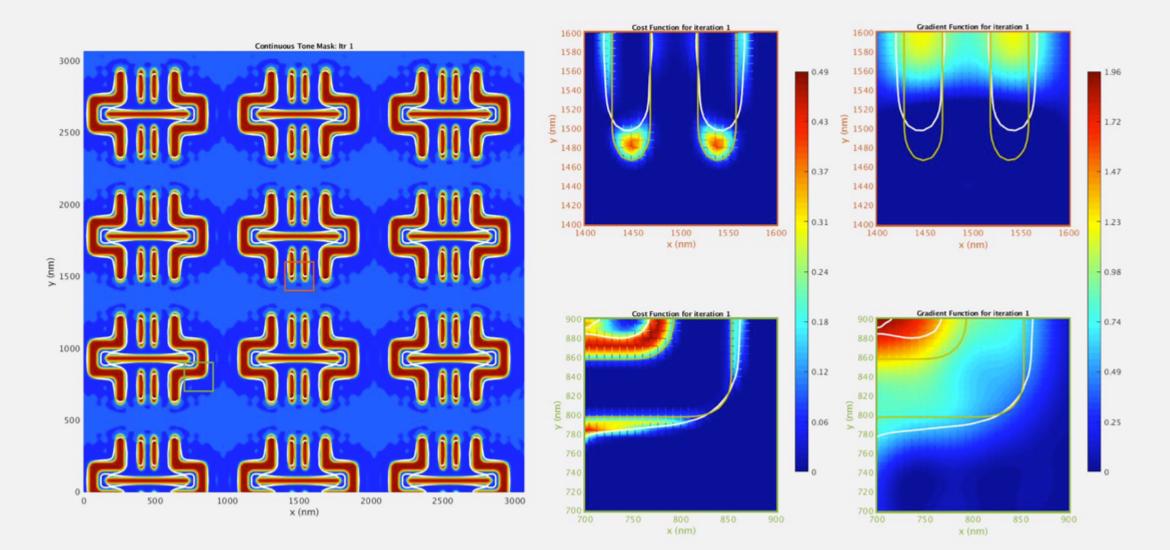

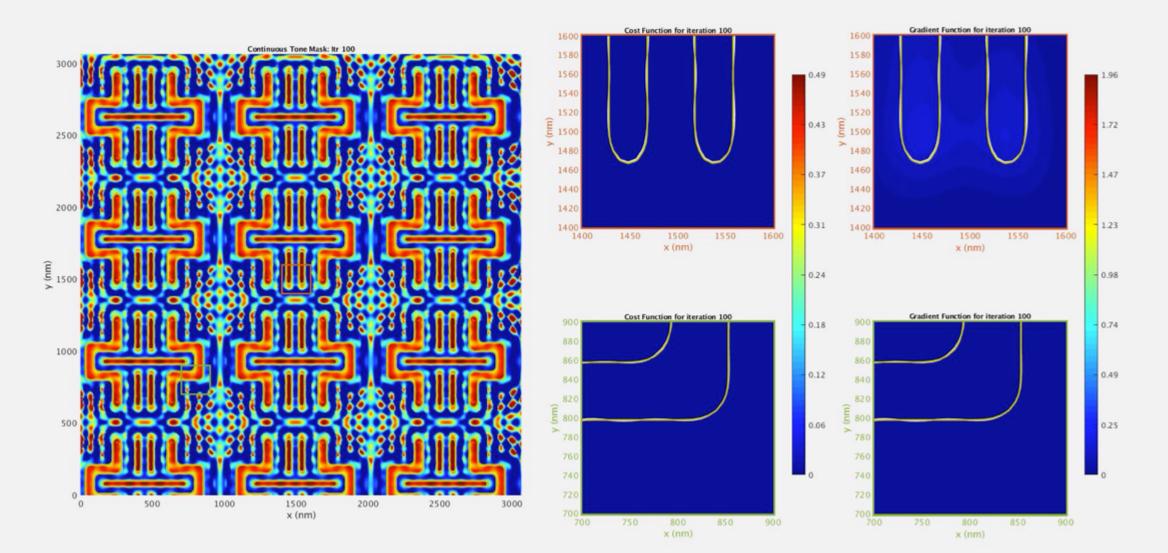

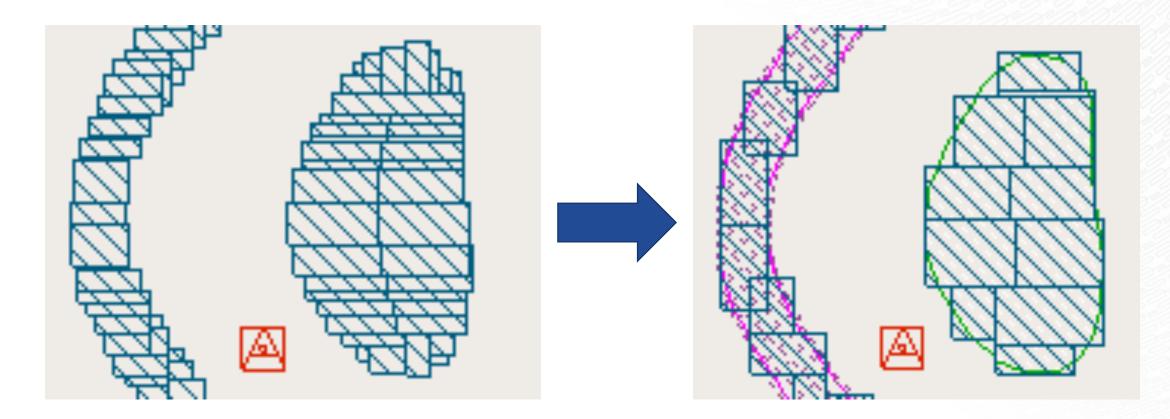

# TrueMask ILT Emulates a Giant CPU/GPU Pair: No Stitching Errors

Conventional ILT: Stitching issues occur when partitions are putting together

TrueMask ILT: The entire chip is updated in each iteration, no stitching issues

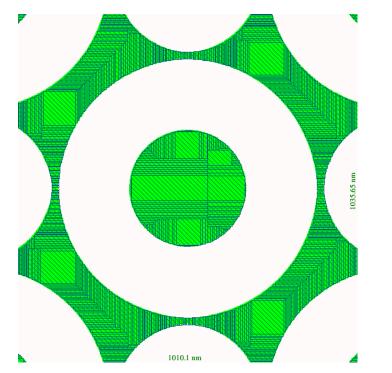

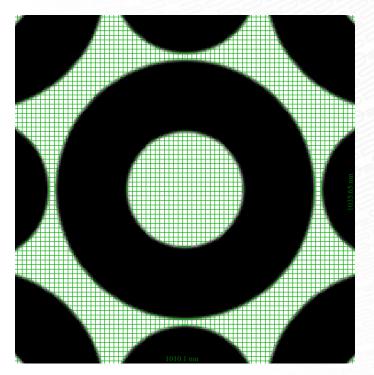

# **TrueMask ILT Integrates Curvilinear Mask Rules to Produce MRC Clean Results**

Without Curvilinear Mask Rules

With Curvilinear Mask Rules

# **TrueMask ILT Meets EPE Requirements**

# **TrueMask ILT Meets EPE Requirements**

# **TrueMask ILT Solutions are Continuous and Symmetric**

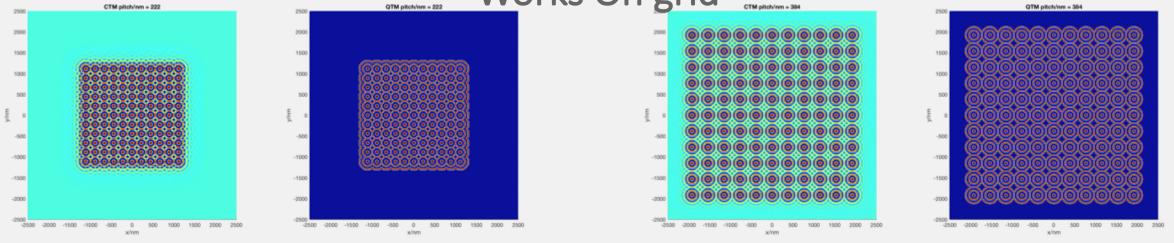

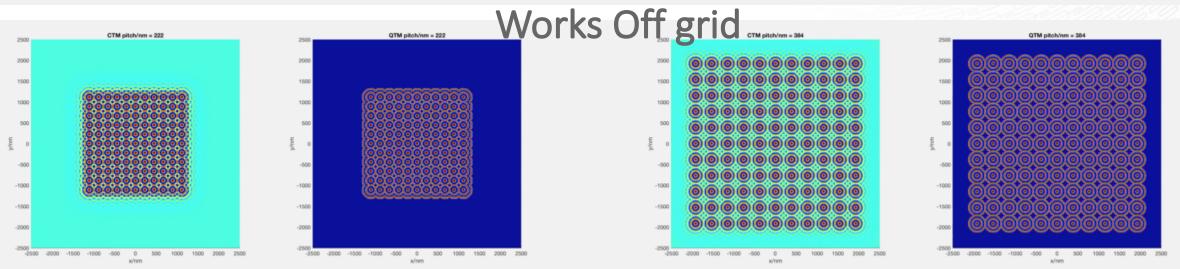

#### TrueMask ILT Solutions are Continuous and Symmetric Works On grid

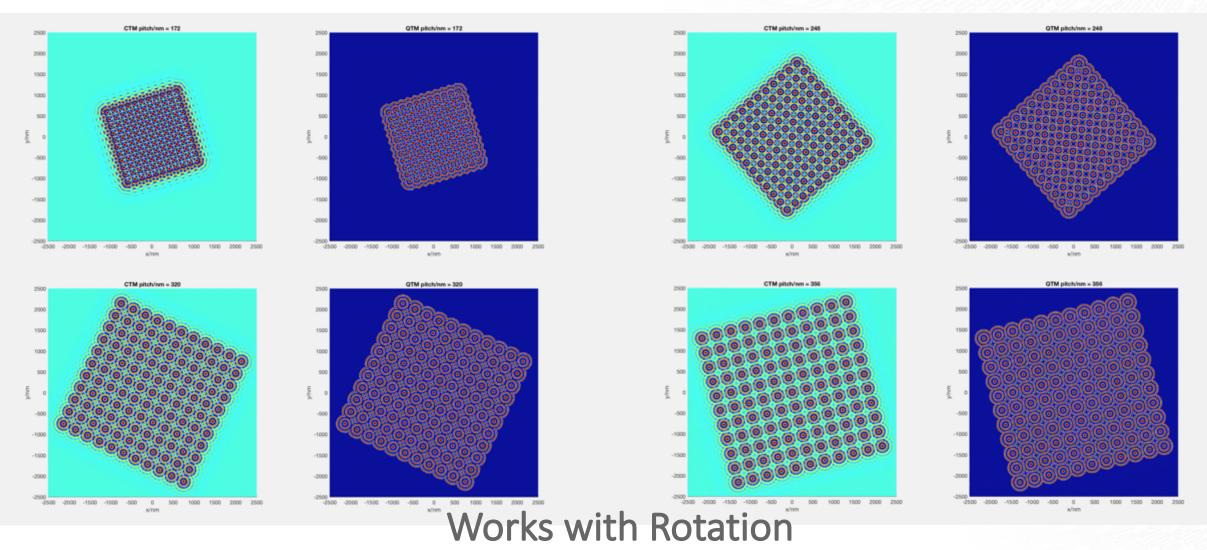

# **TrueMask ILT Solutions are Continuous and Symmetric**

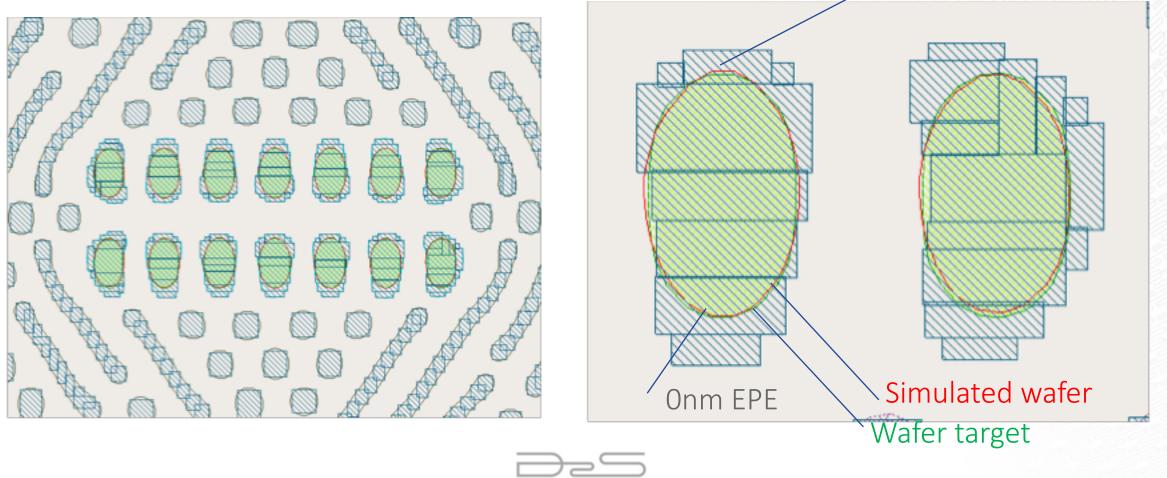

# The End Result: TrueMask ILT Does Full Chip in a Day and Meets All Manufacturing Requirements

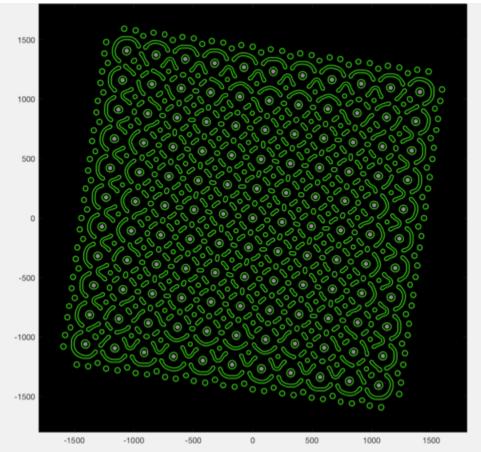

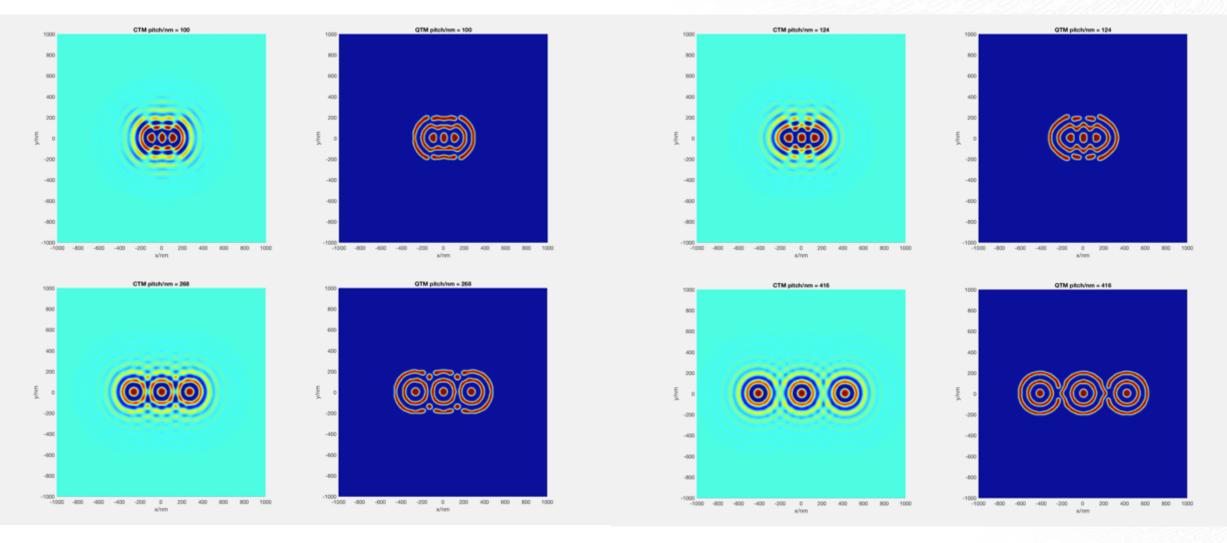

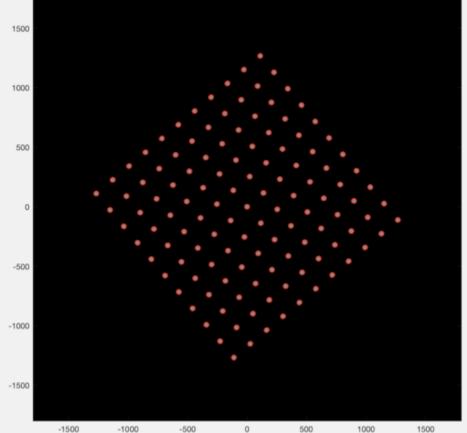

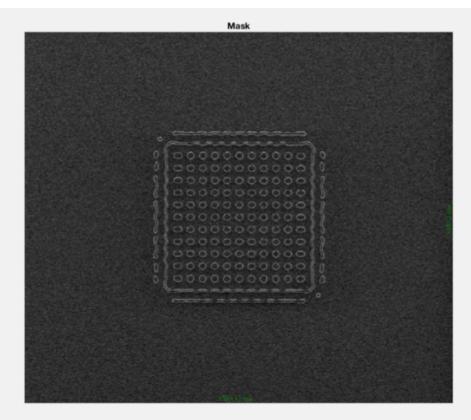

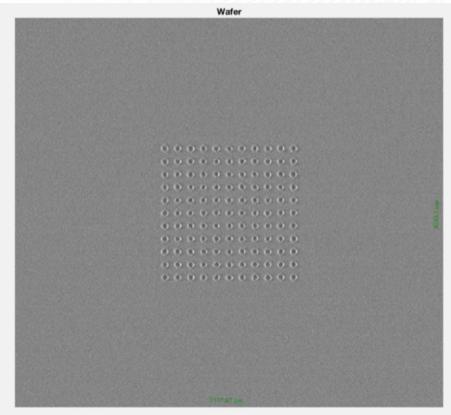

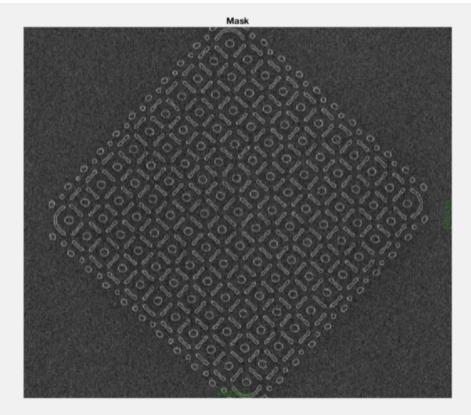

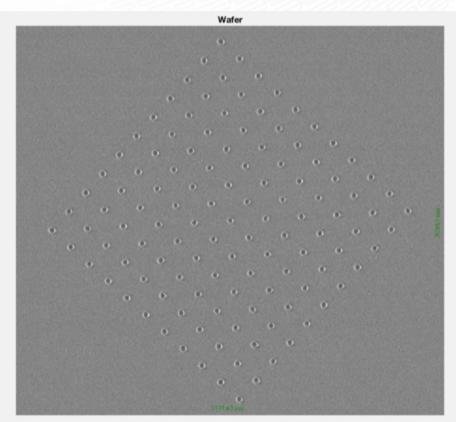

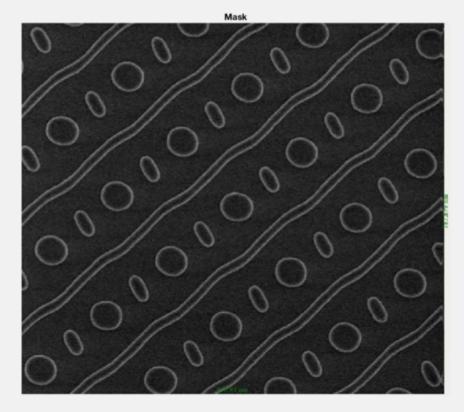

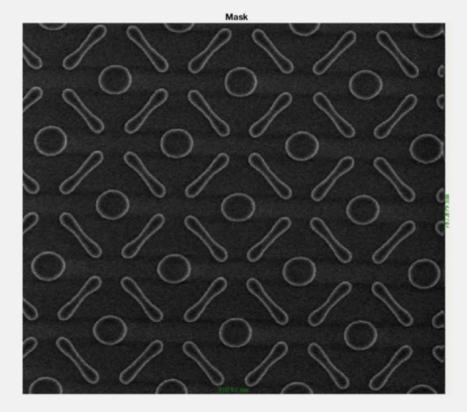

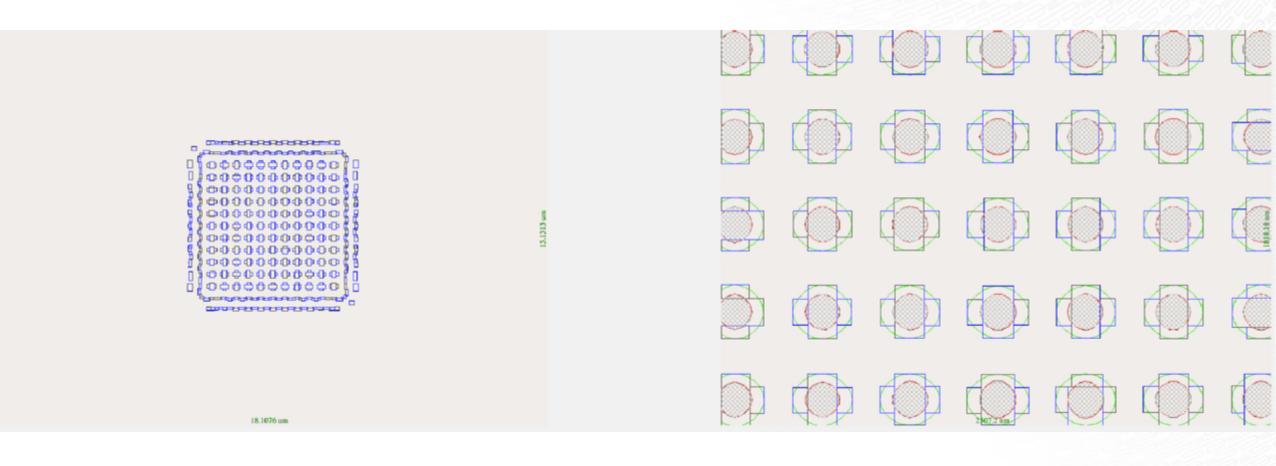

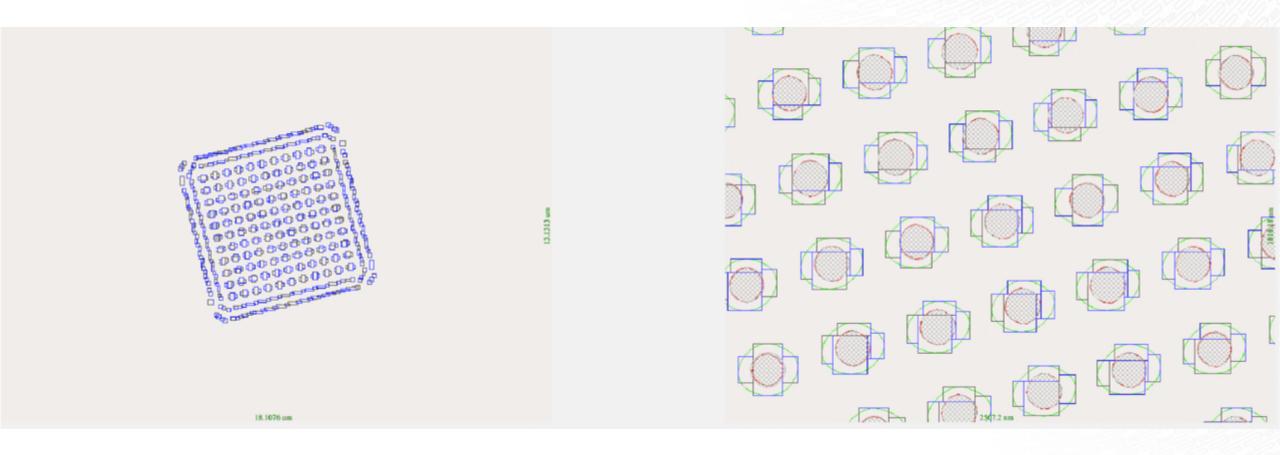

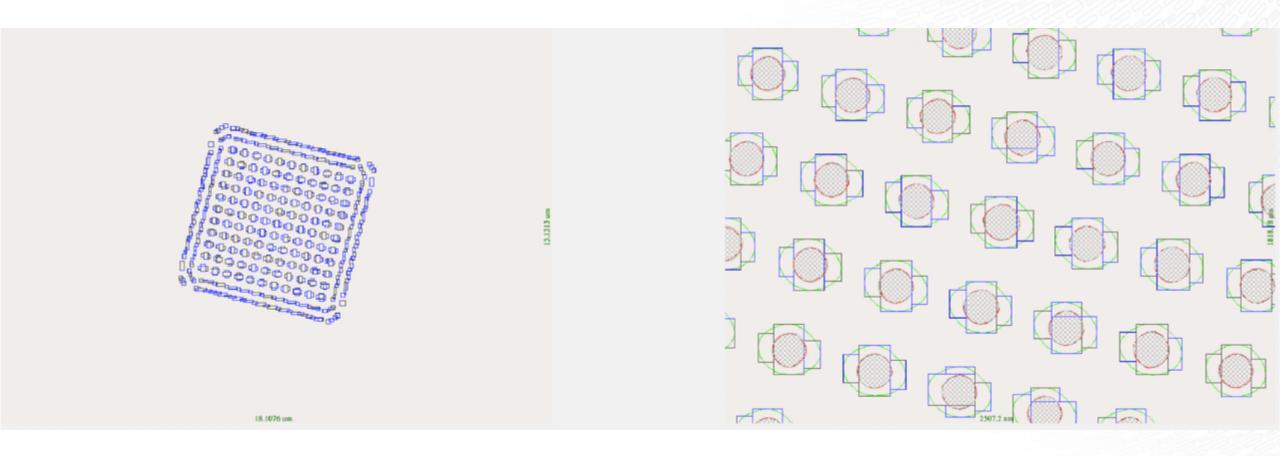

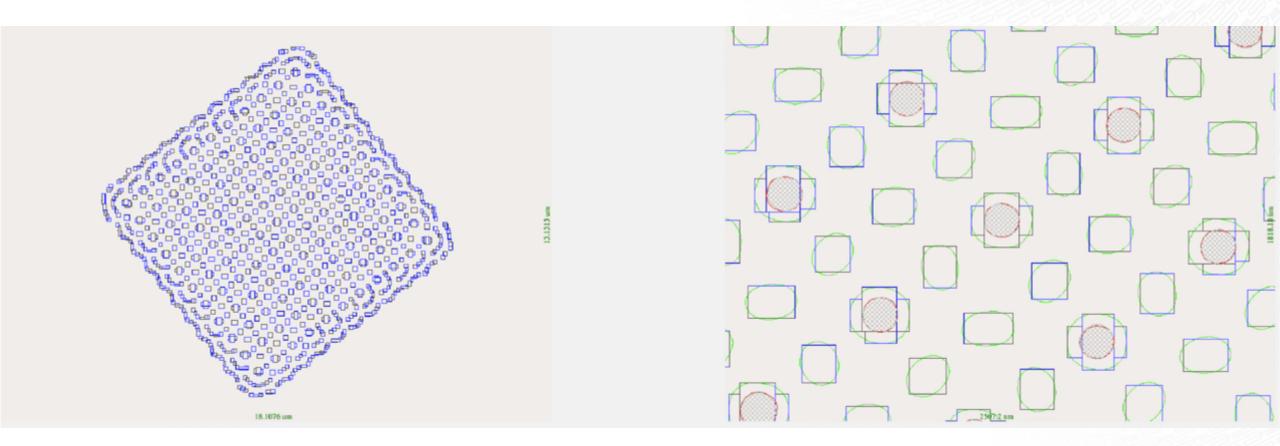

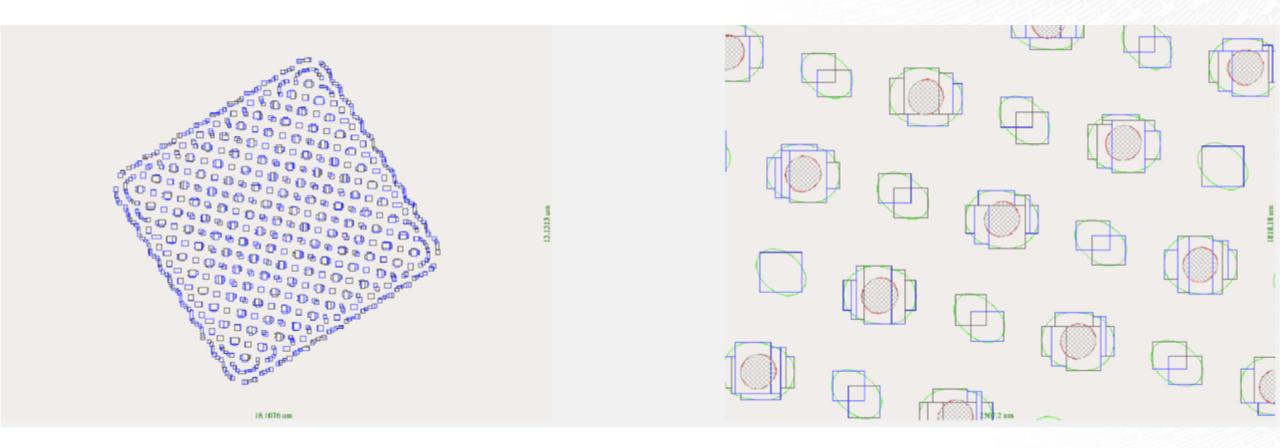

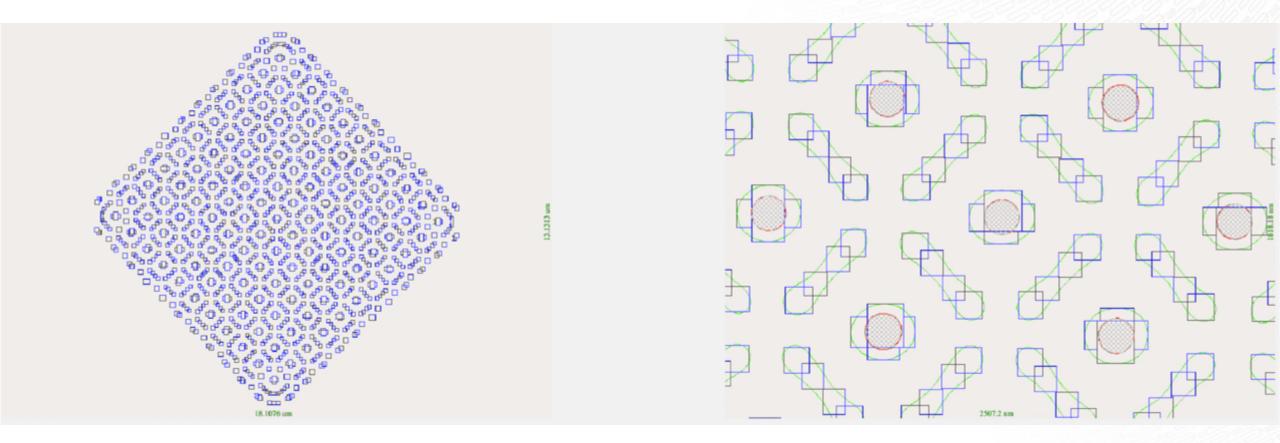

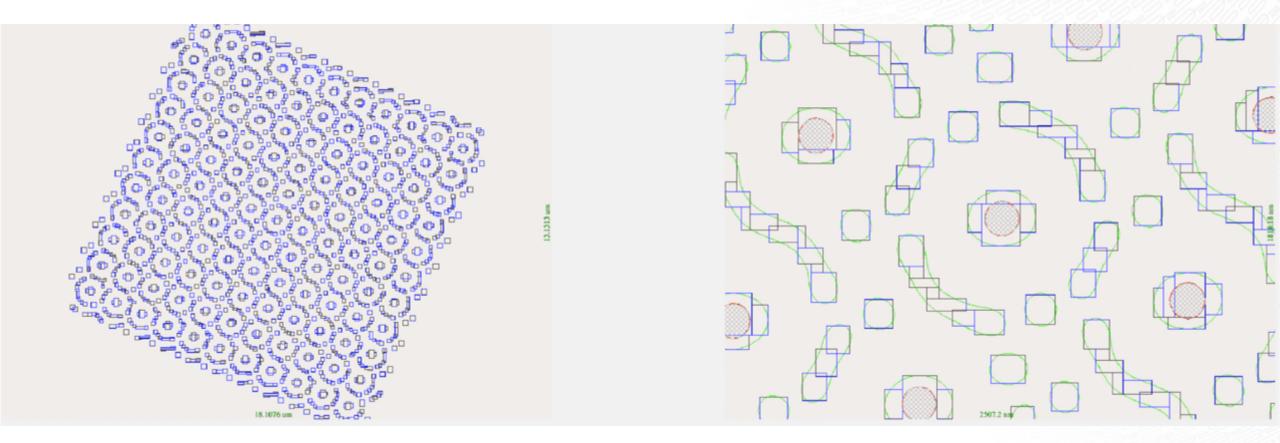

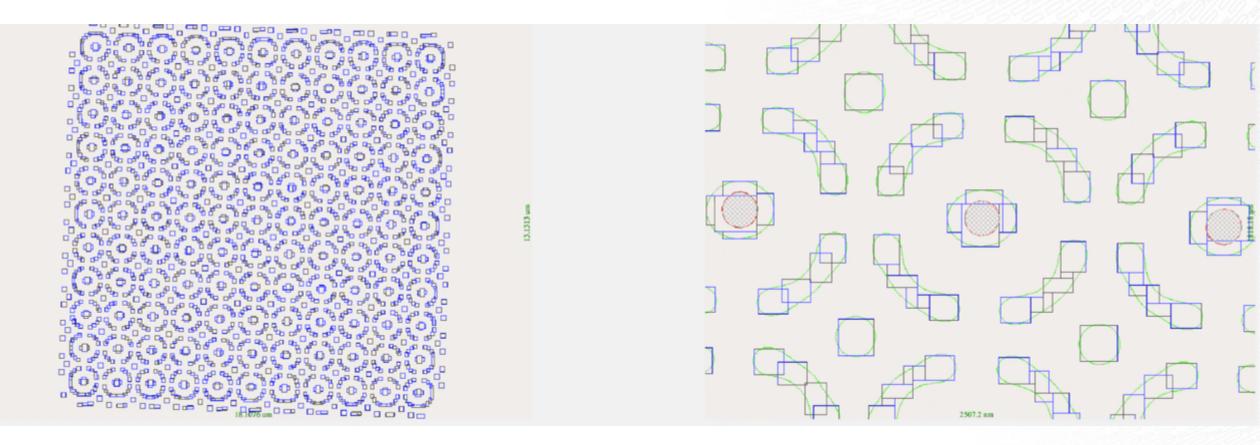

TrueMask ILT curvilinear mask designs for different pitches & orientations

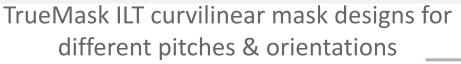

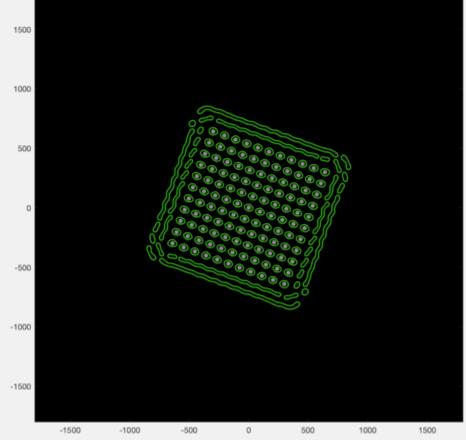

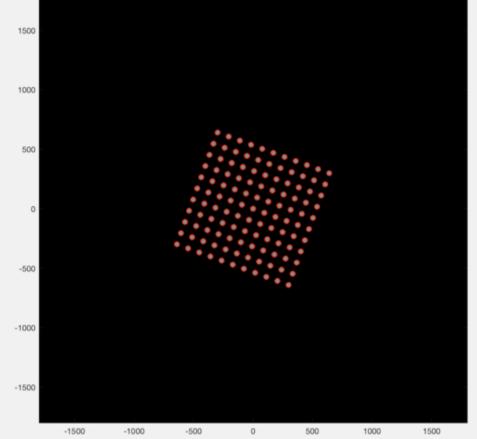

#### Corresponding wafer target & simulated

TrueMask ILT curvilinear mask designs for different pitches & orientations

#### Corresponding wafer target & simulated

D2S PATENTED TECHNOLOGY

TrueMask ILT curvilinear mask designs for different pitches & orientations

Corresponding wafer target & simulated wafer contours

ron

TrueMask ILT curvilinear mask designs for different pitches & orientations

Corresponding wafer target & simulated

wafer contours

ron

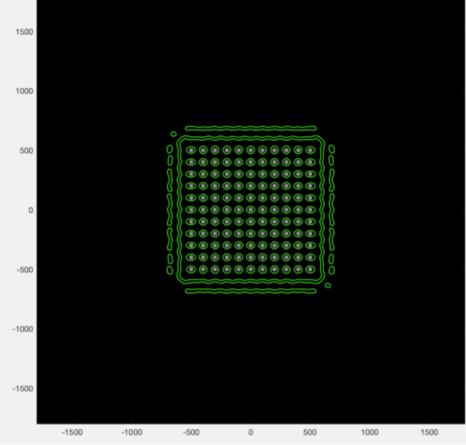

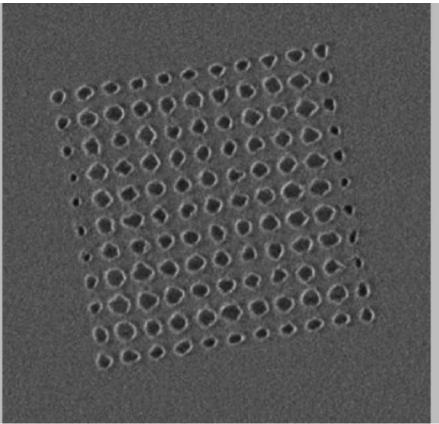

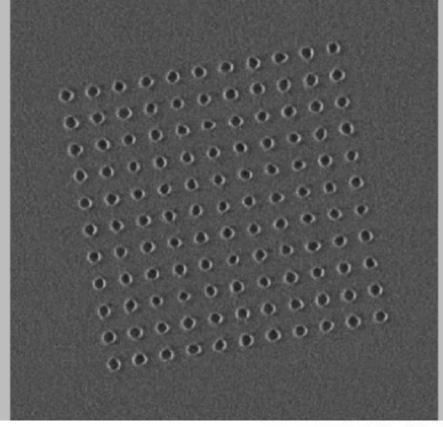

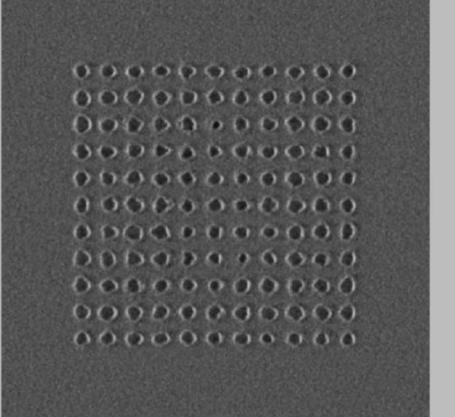

TrueMask ILT curvilinear mask SEM for different pitches & orientations

Mask printed on NuFlare MBM-1000

Corresponding wafer print SEM

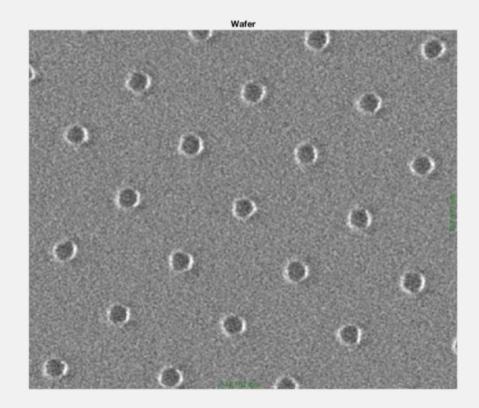

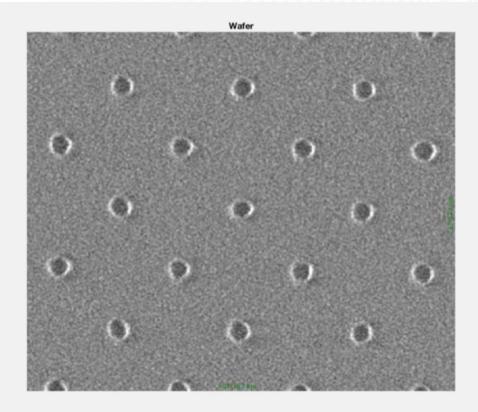

TrueMask ILT curvilinear mask SEM for different pitches & orientations

Mask printed on NuFlare MBM-1000

Corresponding wafer print SEM

TrueMask ILT curvilinear mask SEM for different pitches & orientations

Mask printed on NuFlare MBM-1000

Corresponding wafer print SEM

TrueMask ILT curvilinear mask SEM for different pitches & orientations

Mask printed on NuFlare MBM-1000

Corresponding wafer print SEM

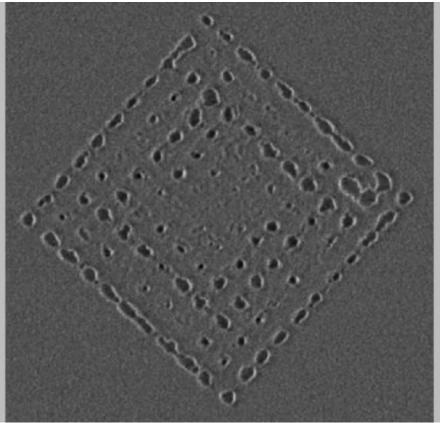

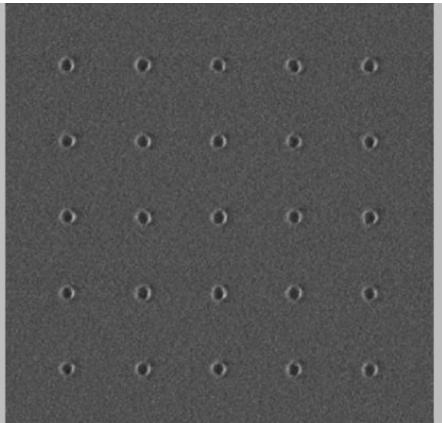

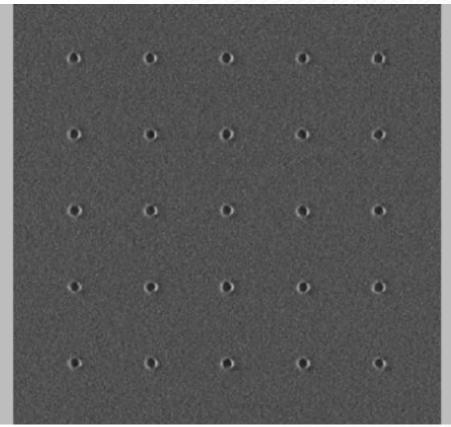

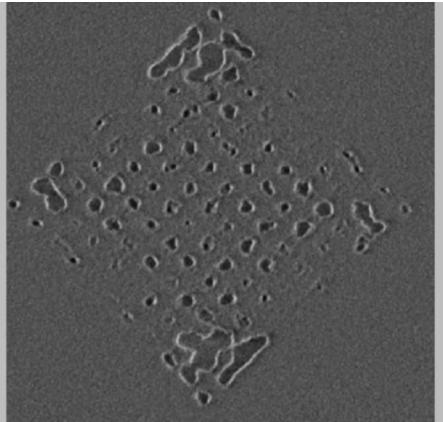

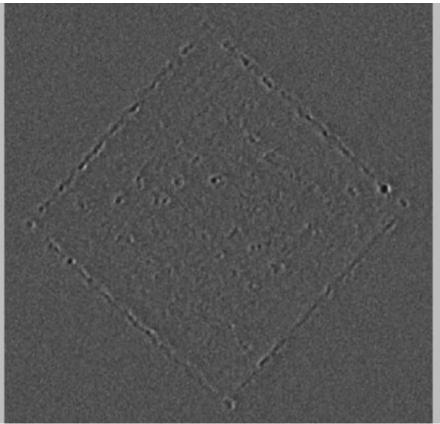

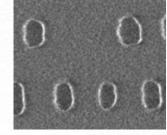

OPC Wafer Print at Different Process Conditions

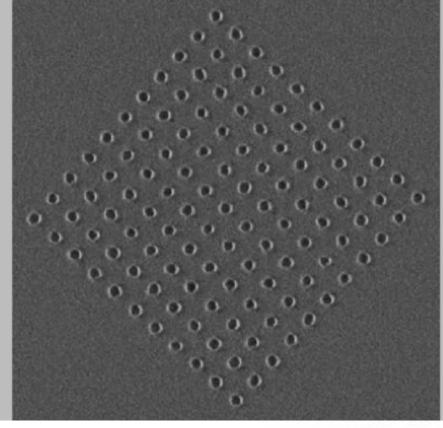

### TrueMask ILT Wafer Print for the Same Process Conditions

TrueMask ILT Wafer Print for the Same Process Conditions

OPC Wafer Print at Different Process Conditions

#### TrueMask ILT Wafer Print for the Same Process Conditions

TrueMask ILT Process Window

#### **OPC Process Window**

| -60nm -40nm -20nm 0nm 20nm 40nm 60nm  |        | -60nm -40nm -20nm 0nm 20nm 40nm 60nm                                                                                 |

|---------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------|

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 93.3%  | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                 |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 95.6%  | 0 00 000 000 000 000 000 000 0<br>0 0 0 0                                                                            |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 97.8%  | 0 00 <mark>0 00</mark> 0 000 000 000 000 000 0<br>10000000000                                                        |

|                                       | 100%   | 0 000 000 000 00 <mark>0 00</mark> 0 000 0<br>1000 000 000 000 000 000 000 000                                       |

| , , , , , , , , , , , , , , , , , , , | 102.2% | 0 000 000 0000 000 000 000 000 000 000                                                                               |

|                                       | 104.4% | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                 |

|                                       | 106.7% | $\circ \circ $ |

| 62.8nm Random Contact                 |        | Green: <10% CD Variation                                                                                             |

Micron

#### 62.8nm Random Contact

**OPC Process Window**

|          | Dose | se Defocus (nm) |      |      |      |      |      | Dose(%) |         |

|----------|------|-----------------|------|------|------|------|------|---------|---------|

|          | (mJ) | -60             | -40  | -20  | 0    | 20   | 40   | 60      | DOSe(%) |

| Latitude | 21   | 55.4            | 59.6 | 62.5 | 61.2 | 60.5 | 51.6 | 41.8    | 93.3%   |

|          | 21.5 | 56.3            | 57.3 | 63.7 | 61.0 | 58.1 | 52.9 | 40.3    | 95.6%   |

|          | 22   | 57.3            | 60.8 | 61.0 | 60.8 | 57.1 | 48.3 | 41.6    | 97.8%   |

|          | 22.5 | 54.0            | 52.8 | 60.1 | 55.8 | 54.7 | 52.1 | 39.3    | 100.0%  |

|          | 23   | 49.4            | 54.4 | 55.3 | 60.3 | 54.5 | 49.2 | 36.1    | 102.2%  |

|          | 23.5 | 49.2            | 50.9 | 54.5 | 55.0 | 51.6 | 46.1 | 33.9    | 104.4%  |

|          | 24   | 54.0            | 56.2 | 54.8 | 49.9 | 50.9 | 44.7 | 28.6    | 106.7%  |

**Best Focus** Norm Dose

60nm Defocus Norm Dose

62.8nm Random Contact

60nm Defocus 93.33% Dose

TrueMask ILT Process Window

|          | Dose | ose Defocus (nm) |      |      |      |      |      | Dose(%) |         |

|----------|------|------------------|------|------|------|------|------|---------|---------|

|          | (mJ) | -60              | -40  | -20  | 0    | 20   | 40   | 60      | Dose(%) |

| Latitude | 21   | 57.7             | 60.5 | 59.6 | 64.1 | 58.8 | 62.1 | 58.4    | 93.3%   |

|          | 21.5 | 54.0             | 56.9 | 58.1 | 60.9 | 59.0 | 62.8 | 59.4    | 95.6%   |

|          | 22   | 60.6             | 55.4 | 59.3 | 60.3 | 57.9 | 59.5 | 58.8    | 97.8%   |

|          | 22.5 | 54.5             | 57.7 | 57.6 | 60.6 | 56.2 | 59.4 | 57.9    | 100.0%  |

|          | 23   | 52.0             | 56.5 | 57.0 | 56.2 | 57.3 | 60.9 | 58.3    | 102.2%  |

|          | 23.5 | 52.2             | 56.7 | 55.1 | 54.6 | 54.9 | 55.6 | 54.7    | 104.4%  |

|          | 24   | 48.6             | 52.7 | 51.6 | 50.8 | 56.1 | 52.3 | 56.1    | 106.7%  |

**Best Focus**

Norm Dose

Norm Dose

60nm Defocus 93.33% Dose

Green: <10% CD Variation

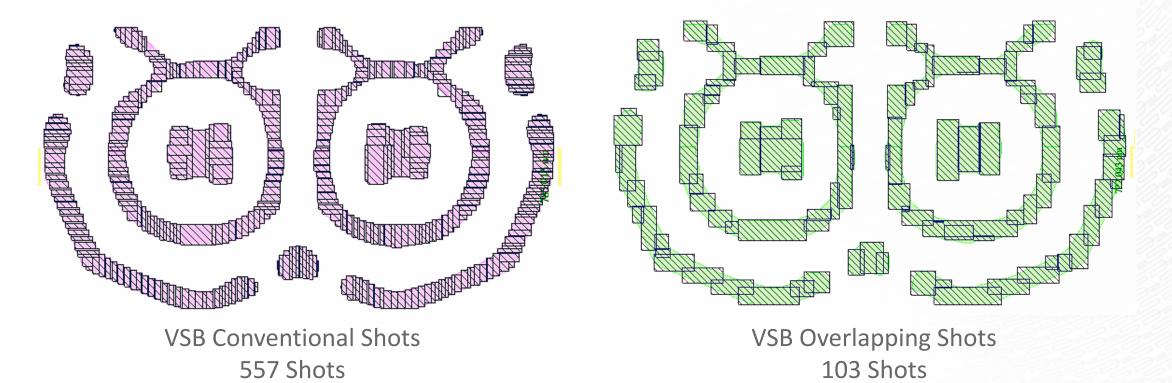

# Is Curvilinear ILT for VSB Mask Writers Hopeless? Or Can Overlapping Shots & Simulation Save the Day?

Majority of shots in this case are SRAFs, not main features SRAFs have little impact on wafer EPE

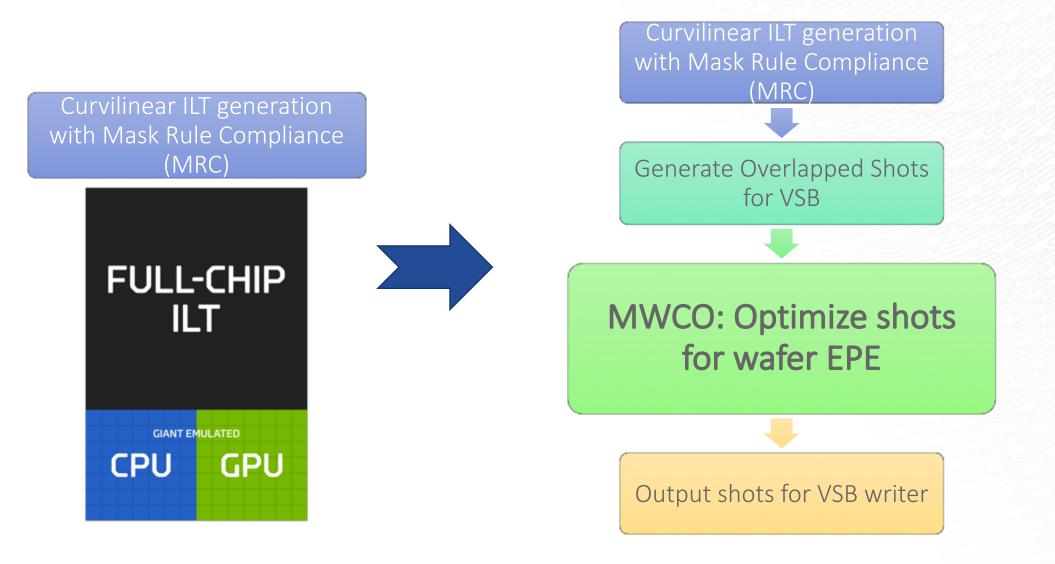

# Mask Wafer Co-Optimization (MWCO) Is the Key

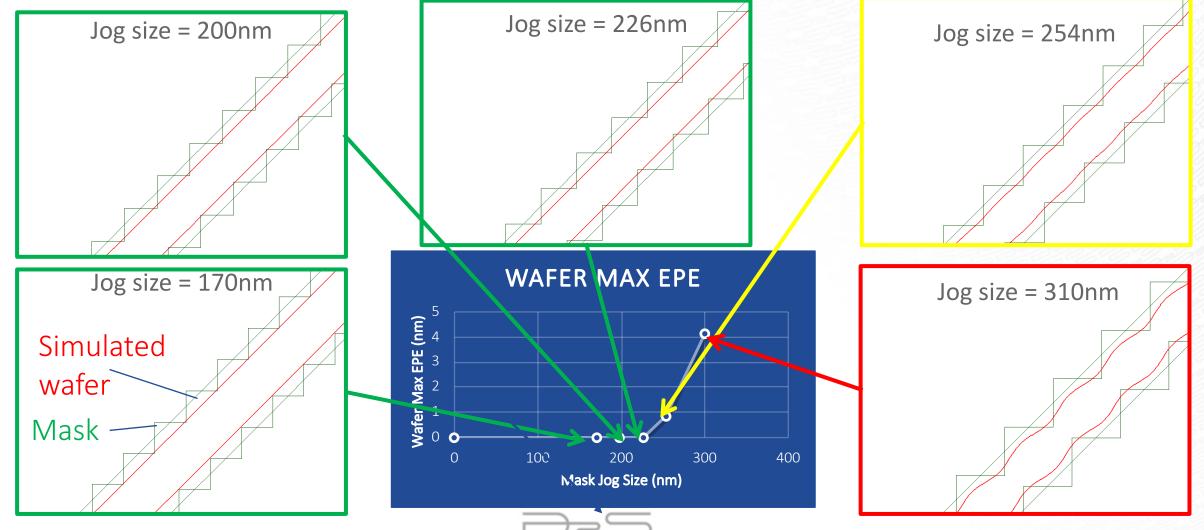

# Small Jogs on Mask Filtered by Band-limited 193i Scanner -Use Bigger Shots & Simulation to Reduce Shot Count

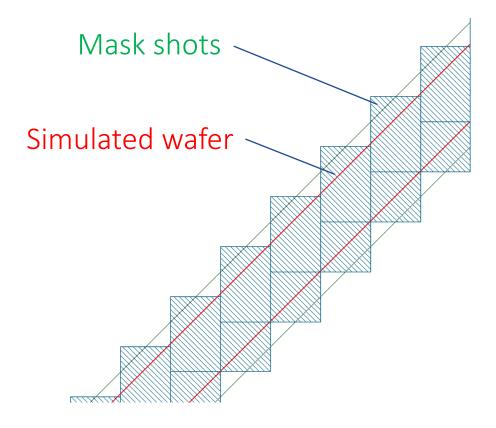

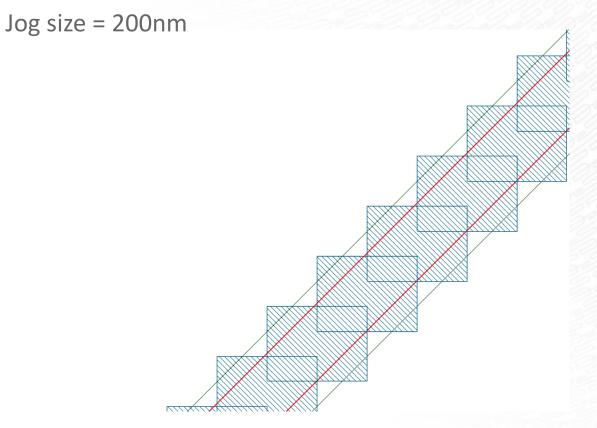

### Overlapping = Fewer Shots for Same Wafer EPE - Use Overlapping Shots and Simulation to Reduce Shot Count

Conventional shots 120 shots, wafer EPE = 0

Overlapping shots 64 shots, wafer EPE = 0

# Balance Shots for Write Time & Mask-Pattern Fidelity Main Features: Conventional, SRAFs: Overlapping

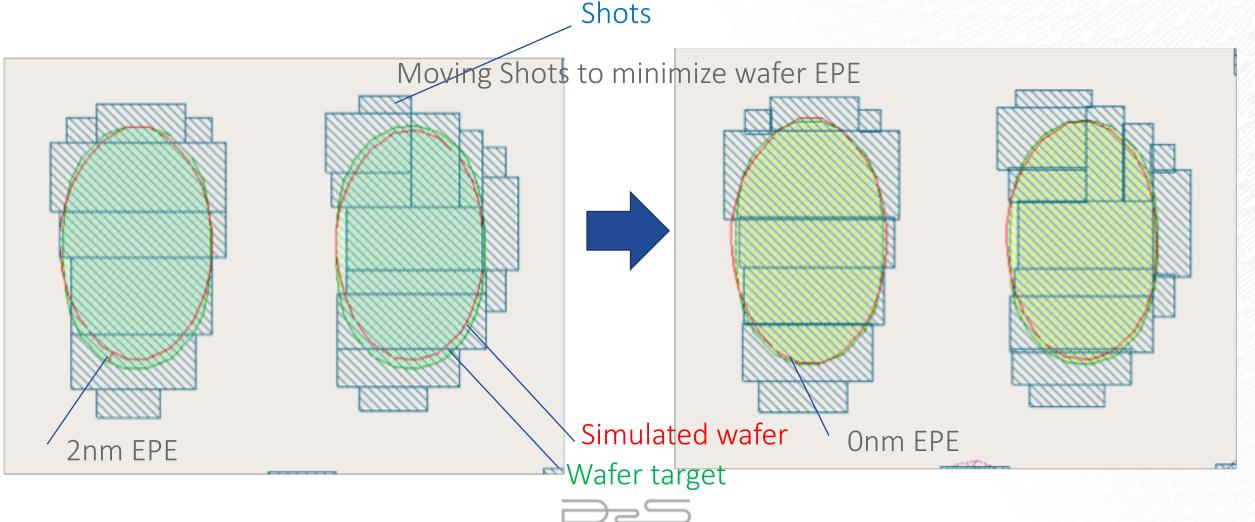

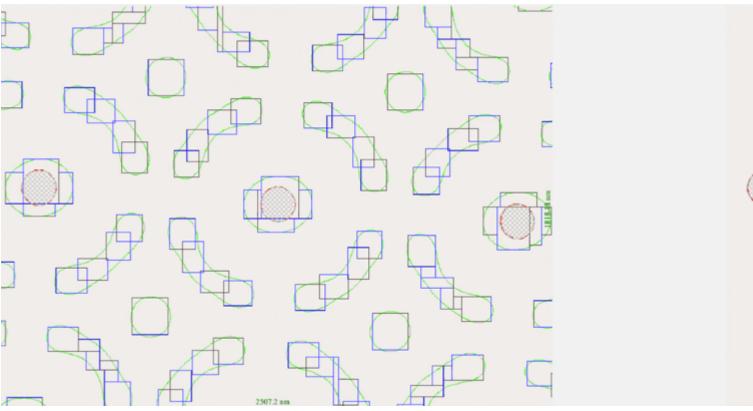

#### MWCO: The Key is to Minimize and Move Shots based on Simulation & Wafer EPE, not Mask Shape

Generate Shots based on Mask EPE \_ Shots

# MWCO: The Key is to Minimize and Move Shots based on Simulation & Wafer EPE, not Mask Shape

#### MWCO: The Key is to Minimize and Move Shots based on Simulation & Wafer EPE, not Mask Shape

Optimize Shots based on wafer EPE \_ Shots

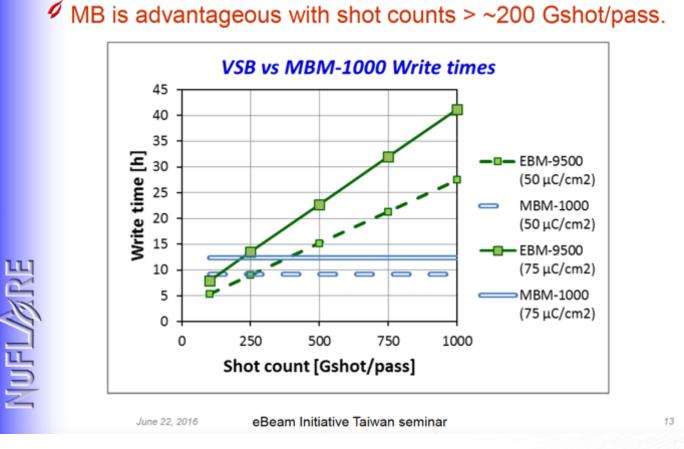

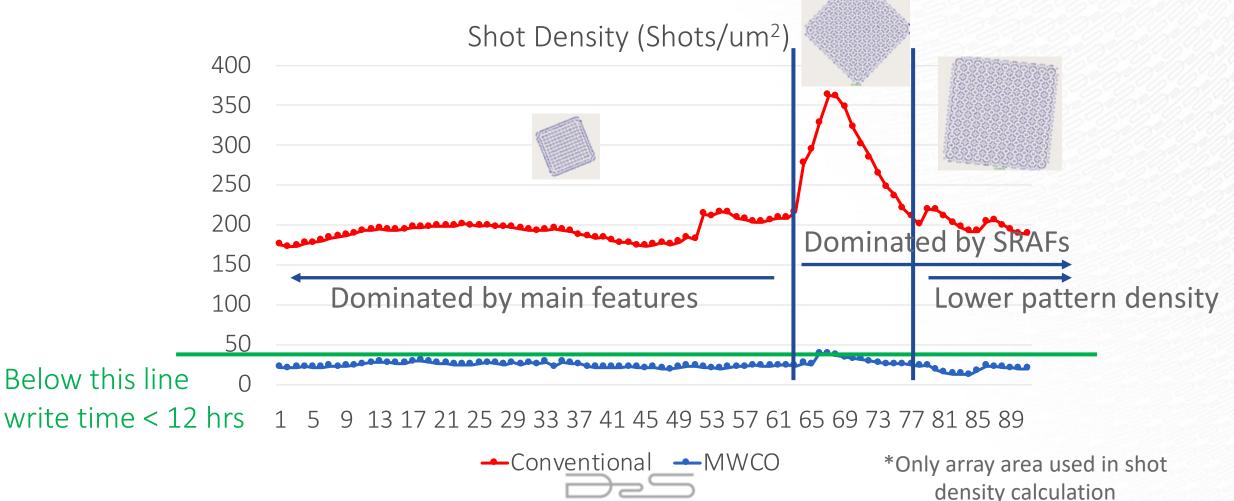

#### VSB Writes Faster than Multi-Beam When Shot Density is Below 36 shots/um<sup>2</sup>

Based on this NuFlare chart, if we want VSB writer to write a mask in less than 12 hours, the average shot density should be <36 shots/um<sup>2</sup>

# Full Curvilinear ILT Mask w' MWCO can be Written within 12 Hrs on VSB Writer – Less Write Time than Multi-Beam

# TrueMask<sup>®</sup> ILT MWCO: Full-Chip Curvilinear ILT in a Day & VSB Writing in 12 hours for 193i

# TrueMask<sup>®</sup> ILT MWCO: Full-Chip Curvilinear ILT in a Day & VSB Writing in 12 hours for 193i

# TrueMask<sup>®</sup> ILT MWCO: Full-Chip Curvilinear ILT in a Day & VSB Writing in 12 hours for 193i

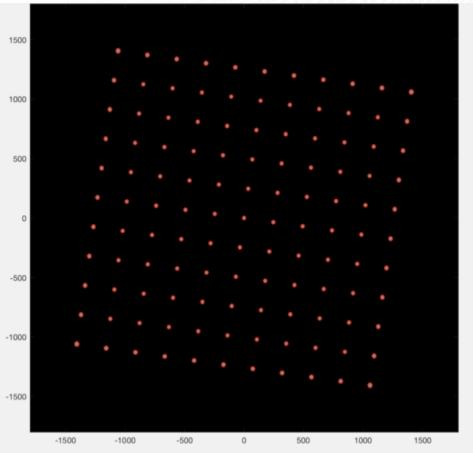

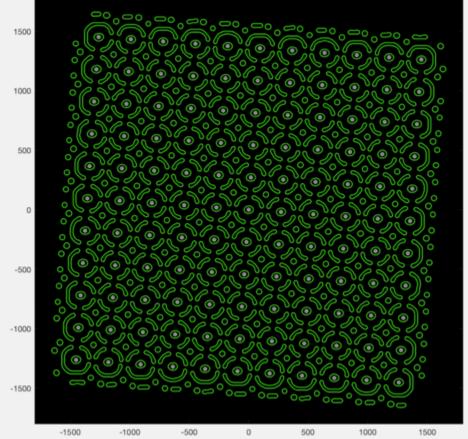

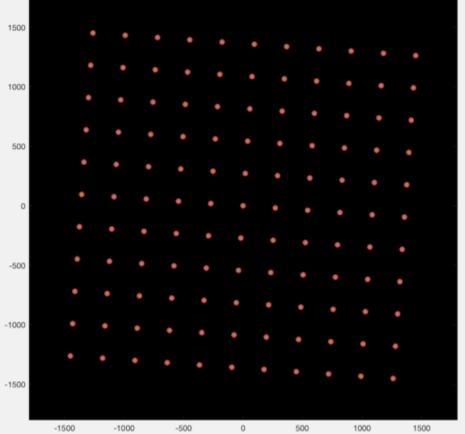

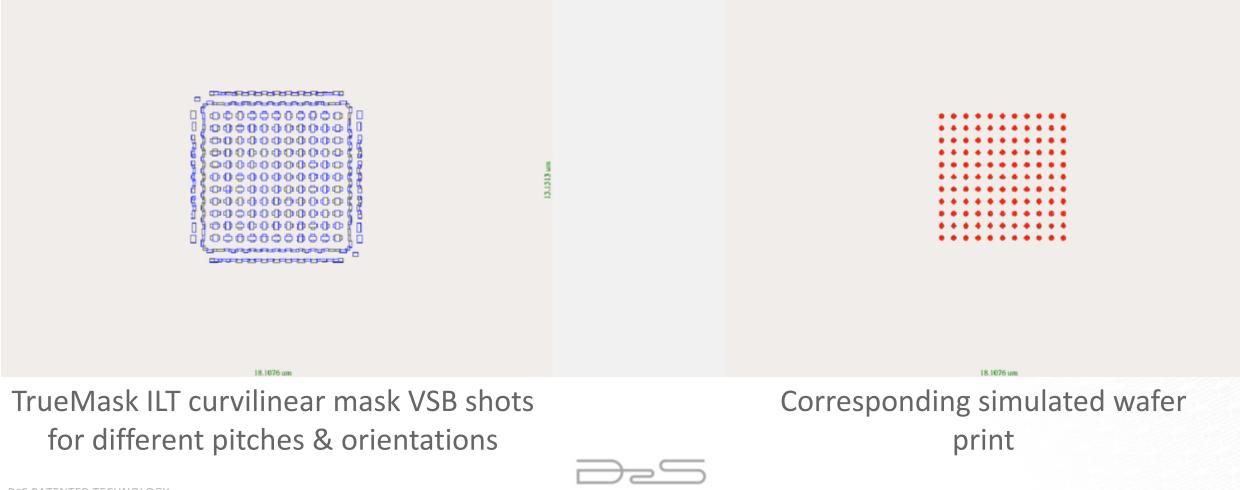

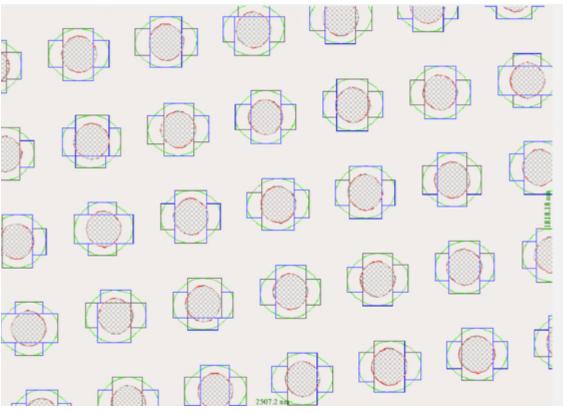

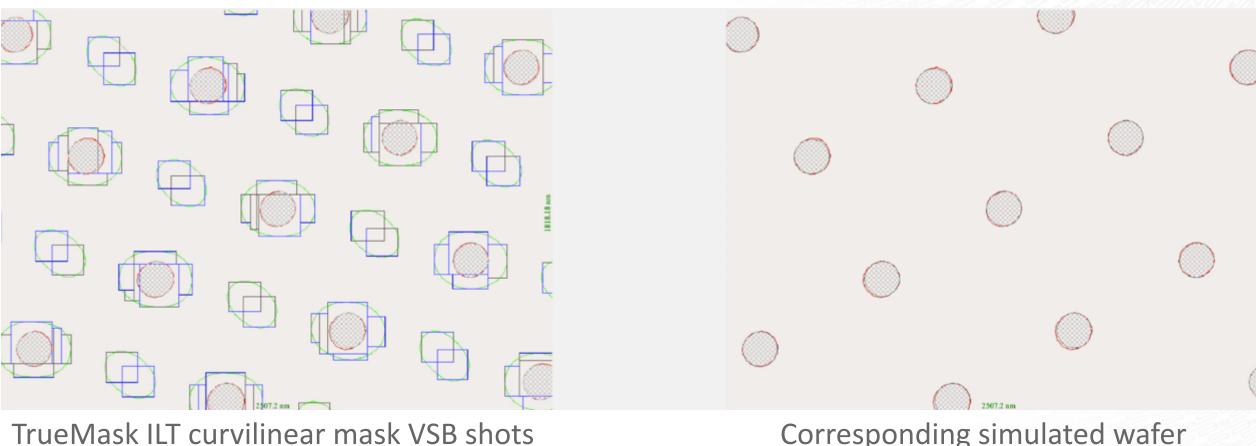

TrueMask ILT curvilinear mask VSB shots for different pitches & orientations

# TrueMask<sup>®</sup> ILT MWCO: Full-Chip Curvilinear ILT in a Day & Full Mask Multi-Beam and VSB Writing in 12 hrs for 193i

TrueMask ILT curvilinear mask VSB shots for different pitches & orientations

Corresponding simulated wafer print

# TrueMask<sup>®</sup> ILT MWCO: Full-Chip Curvilinear ILT in a Day & Full Mask Multi-Beam and VSB Writing in 12 hrs for 193i

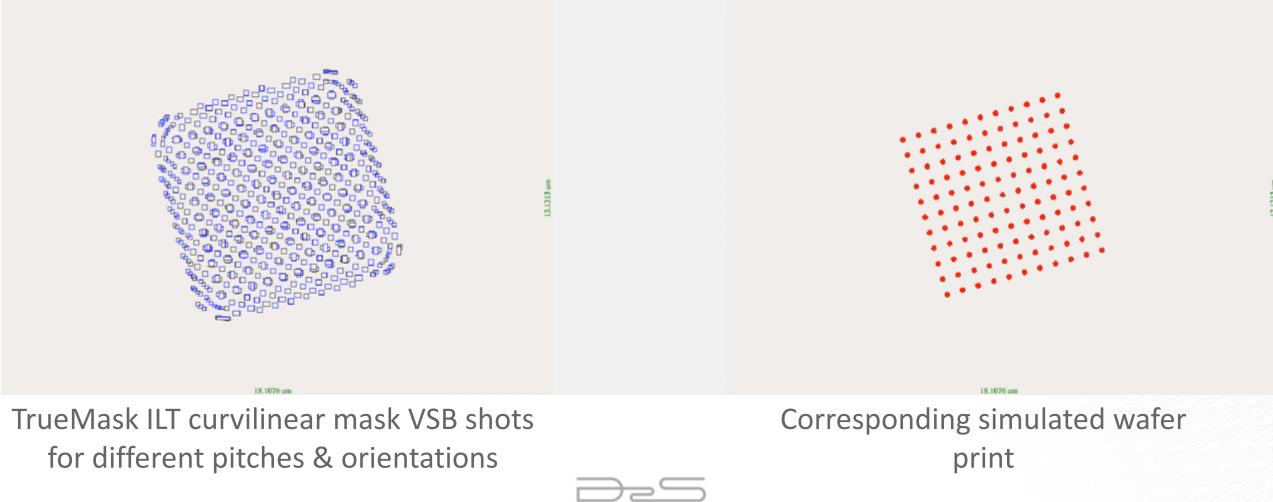

for different pitches & orientations

### TrueMask<sup>®</sup> ILT MWCO: Full-Chip Curvilinear ILT in a Day & Full Mask Multi-Beam and VSB Writing in 12 hrs for 193i

Corresponding simulated wafer print

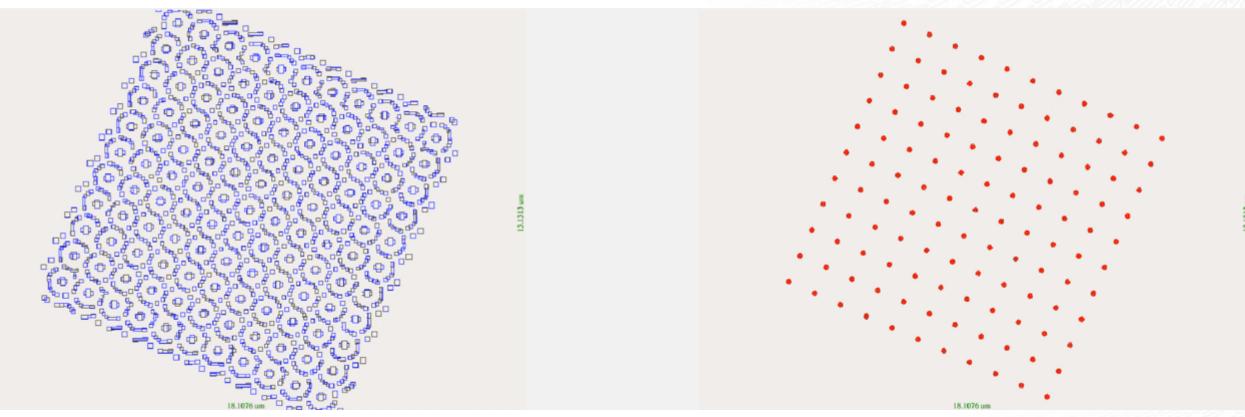

TrueMask ILT curvilinear mask VSB shots for different pitches & orientations

# $\rightarrow$

Thanks to NuFlare for their help to write the curvilinear masks with MBM-1000

Thanks to ASML for their help to acquire wafer images with eP5 platform

ASML