# **PROCEEDINGS OF SPIE**

SPIEDigitalLibrary.org/conference-proceedings-of-spie

# Enabling faster VSB writing of 193i curvilinear ILT masks that improve wafer process windows for advanced memory applications

Pang, Linyong (Leo), Russell, Ezequiel, Baggenstoss, Bill, Lu, Yang, Lee, Michael, et al.

Linyong (Leo) Pang, Ezequiel V Russell, Bill Baggenstoss, Yang Lu, Michael Lee, Jennefir Ping Digaum, Ming-Chuan Yang, Ryan Pearman, P. Jeffrey Ungar, Lu Sha, Ali Bouaricha, Michael Pomerantsev, Mariusz Niewczas, Kechang Wang, Bo Su, Michael Meyer, Aki Fujimura, "Enabling faster VSB writing of 193i curvilinear ILT masks that improve wafer process windows for advanced memory applications," Proc. SPIE 11518, Photomask Technology 2020, 115180W (7 October 2020); doi: 10.1117/12.2579729

Event: SPIE Photomask Technology + EUV Lithography, 2020, Online Only

## Enabling Faster VSB Writing of 193i Curvilinear ILT Masks That Improve Wafer Process Windows for Advanced Memory Applications

Linyong (Leo) Pang<sup>1</sup>, Ezequiel Vidal Russell<sup>2</sup>, Bill Baggenstoss<sup>2</sup>, Yang Lu<sup>2</sup>, Michael Lee<sup>2</sup>, Jennefir Digaum<sup>2</sup>, Ming-Chuan Yang<sup>2</sup>, Ryan Pearman<sup>1</sup>, P. Jeffrey Ungar<sup>1</sup>, Lu Sha<sup>1</sup>, Ali Bouaricha<sup>1</sup>, Michael Pomerantsev<sup>1</sup>, Mariusz Niewczas<sup>1</sup>, Kechang Wang<sup>1</sup>, Bo Su<sup>1</sup>, Michael Meyer<sup>1</sup>, Aki Fujimura<sup>1</sup> <sup>1</sup>D2S, Inc. (US) <sup>2</sup> Micron Technology, Inc. (US) <sup>1</sup>4040 Moorpark Avenue, Suite 250, San Jose, CA 95117 USA <sup>2</sup>8000 South Federal Way, Post Office Box 6, Boise, Idaho 83707-0006

#### ABSTRACT

In advanced semiconductor memory manufacturing, mask and lithography are critical for patterning. In this paper we jointly study the benefits of a full-chip, curvilinear, stitchless inverse lithography technology (ILT) with mask-wafer cooptimization (MWCO) for memory applications. The full-chip ILT technology employed in this study, first demonstrated in a paper presented at the 2019 SPIE Photomask Technology Conference[20], produces curvilinear ILT mask patterns without stitching errors, and with process windows enlarged by over 100% compared to the OPC process of record. At the 2020 SPIE Advanced Lithography conference, a new method was introduced, in which mask-wafer co-optimization (MWCO) is performed during ILT optimization[22]. This new approach enables curvilinear ILT for 193i masks to be written on variable-shaped beam (VSB) mask writers within a practical, 12-hour time frame, while also producing the largest process windows. This new study presents the mask and wafer results using MWCO. Curvilinear ILT mask patterns written by VSB mask writer and the corresponding 193i process wafer prints are shown. Evaluations of mask write times, and mask quality in terms of CD uniformity and process windows are also presented.

**Keywords:** Photomask, GPU, Inverse Lithography Technology, ILT, Curvilinear ILT, Mask Wafer Co-Optimization (MWCO), Multi-beam Mask Writer, VSB Mask Writer, MDP, MPC

#### 1. INTRODUCTION

#### 1.1 Full-Chip, Curvilinear ILT is Now a Practical Reality

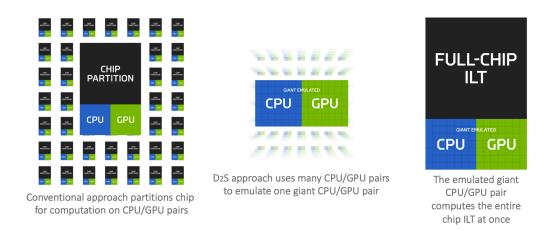

Inverse lithography technology (ILT) – a mathematically rigorous inverse approach that determines the mask shapes that will produce the desired on-wafer results – has been seen as a promising solution to many of the challenges of advancednode lithography, whether optical or EUV. Since its introduction more than a decade ago [1-17], there have been numerous studies that demonstrate that curvilinear ILT mask shapes, in particular, produce the best process windows [18]. However, until recently, the runtimes associated with this computational technique have limited its practical application to critical "hotspots" on chips [19]. The solution to the runtime problem for ILT has been particularly vexing, as the traditional approach to runtime improvement – partitioning and stitching – has failed to produce satisfactory results, either in terms of runtime or in terms of quality. At the 2019 SPIE Photomask Technology Conference [20], we detailed an entirely new, stitchless approach, creating a purpose-built system for ILT, called TrueMask<sup>®</sup> ILT. This system includes a unique GPU-accelerated approach that emulates a single, giant GPU/CPU pair that can compute an entire full-chip ILT solution at once, in a single day (Figure 1). This novel approach, systematically designed for ILT and GPU acceleration, made full-chip ILT a practical reality in production for the first time.

Photomask Technology 2020, edited by Moshe E. Preil, Proc. of SPIE Vol. 11518, 115180W · © 2020 SPIE · CCC code: 0277-786X/20/\$21 · doi: 10.1117/12.2579729

Figure 1: TrueMask ILT, although comprising many GPU/CPU pairs, has been holistically designed so that it behaves as a single GPU/CPU pair, iterating on the entire chip as a whole, and avoiding stitching errors

The 2019 paper details how TrueMask ILT meets all of the requirements for a production-ready full-chip, curvilinear ILT solution: it integrates curvilinear mask rules to produce mask-rule-checking (MRC)-clean results; it meets edge-placement error (EPE) requirements; its results are continuous and symmetric; it demonstrates both on-grid and off-grid invariance; it is symmetric from any angle.

To validate TrueMask ILT results, D2S worked with Micron Technology to write masks and print wafers using the Micron Technology process of record (POR) [20, 21]. The ultimate goal for curvilinear ILT is to achieve the best process window, so in this evaluation, process windows were compared between OPC and TrueMask ILT using the Micron POR. Critical dimensions (CDs) were measured to quantify the size of the process window between OPC and TrueMask ILT.

Figure 2 shows the wafer-print matrix result for a random contact layer. These are all cases where the contacts are arranged in a Manhattan layout, without introducing non-orthogonal configurations. The target CD was 62.8nm; all dies with CD within a 10% variation are considered to be within the required process window. The CD measurements that meet the conditions within the process window are highlighted in green in the chart. Notice that the x axis is the focus, y axis is the dose (to be consistent with the process window plot). Three wafer images at the process center and two process corners are also shown below the charts. Compared to the Micron POR OPC, TrueMask ILT enlarged the process window by over 100%.

| OPC Process Window                    | IrueMask ILI Process Window                                                                                          |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| -60nm -40nm -20nm 0nm 20nm 40nm 60nm  | -60nm -40nm -20nm 0nm 20nm 40nm 60nm                                                                                 |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                 |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                 |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0    0 0    0 0 0   0 0 0    0 0 0    0 0                                                                            |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0    000    000    000    000    000                                                                                 |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                 |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                 |

|                                       | $\circ \circ $ |

### ODC Due a ser M/Ser discus

Ture Marshall HT Due ere a MA/Surahawa

Figure 2: Process window CD measurements for standard OPC vs. TrueMask ILT of Micron Technology's POR. The green regions are within process window. Random contact target CD is 62.8nm. 10% CD variation is used for process window criteria. TrueMask ILT increases the process window by more than 100% [20].

#### 1.2 Could This Full-Chip ILT Approach Be Extended to VSB Mask Writing?

The approach detailed in the 2019 paper relied on multi-beam mask writing, an important new development in mask writing that is pixel-based, rather than shape-based, and so is shape-agnostic in terms of write-time. The question that remained was if the benefits of full-chip, curvilinear ILT could be extended to the masks created by VSB mask writers that make up the majority of equipment in the mask-shops around the world today. For 193i processing, advanced nodes need as much edge-placement accuracy as possible. The improved process windows that are possible from curvilinear ILT can help greatly. This is why it is important to enable curvilinear ILT for 193i to be written on widely available VSB mask writers.

In the 2020 paper, we detailed a mask-wafer co-optimization (MWCO) method that in combination with established techniques, such as overlapping shots and mask and wafer simulation, creates Manhattanized, full-chip, curvilinear ILT mask shapes that VSB mask writers can write within 12 hours[22]. This paper will validate those results on real mask and wafer prints using VSB mask writing for 193i.

#### 2. MASK-WAFER CO-OPTIMIZATION FOR FULL-CHIP CURVILINEAR ILT FOR VSB MASK WRITERS

#### 2.1 Mask Data Preparation and Mask Process Correction for Curvilinear ILT Masks

The conventional approach to Manhattanizing curvilinear ILT masks requires a trade-off of accuracy for ILT runtime and the write time on the VSB mask writer. It is possible to get very close to a curvilinear target using many small rectilinear mask shapes to form curves with small "jogs" or "stair-steps." This approach creates fairly good curvilinear mask shapes using VSB writers. However, the shot count involved in this approach would lead to impractical write-times if it were to be used on a full-chip ILT design. Alternatively, jog and step-sizes can be made larger, say 20nm, to limit VSB shot count, but even then, if practiced at a full-chip scale, write times would be prohibitive using conventional fracturing (without overlapping shots). This practical reality, combined with the long runtimes of the traditional ILT software, even when running on a large bank of CPUs, has limited the use of ILT to small "hotspots." Yet the need to run ILT for hotspots suggests that there is general understanding that ILT produces superior process windows for the wafer.

#### 2.2 Overlapping Shots and Simulation Enable Full-Chip, Curvilinear ILT Using VSB Mask Writers

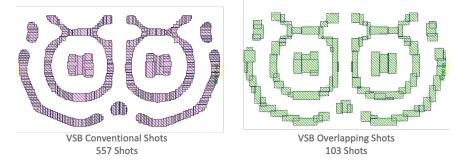

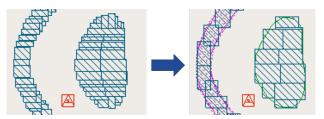

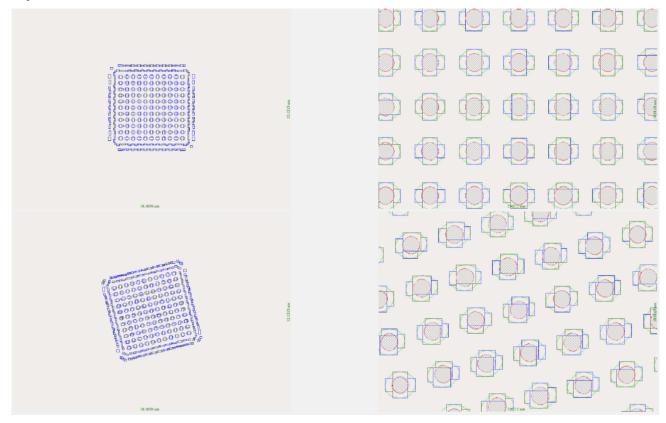

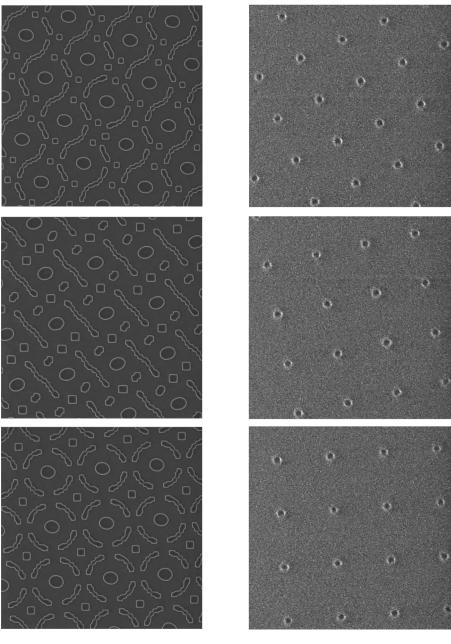

Overlapping shots is a technique to reduce shots and improve dose margin for angled lines and curvilinear features to be written by VSB mask writers [23, 24]. Figure 3 shows a typical curvilinear ILT mask pattern, fractured for a VSB mask writer. The pattern on the left uses conventional MDP for VSB; the pattern on the right, employs MDP with overlapping shots to create the same pattern. There are two observations from this example: first, overlapping shots can significantly reduce total shot count; and second, the majority of shots in this case (and in most production designs) are for the sub-resolution assist features (SRAFs) – which do not print – not for the main features. As we know, SRAFs have far less impact on the wafer edge-placement error (EPE) as compared to main features. For any given target main feature in a contact layer, an overwhelming number of shots are used for the SRAFs in a conventionally fractured solution. Overlapping shots produce SRAFs that perform well without devoting so much of the VSB write-time to producing them.

Figure 3: Example of a curvilinear ILT mask pattern written by VSB mask writer with conventional (fracturing) shots and overlapping shots.

#### 2.3 Mask Wafer Co-Optimization (MWCO) Shifts the OPC and Mask Shop Hand-off to Mask Shots

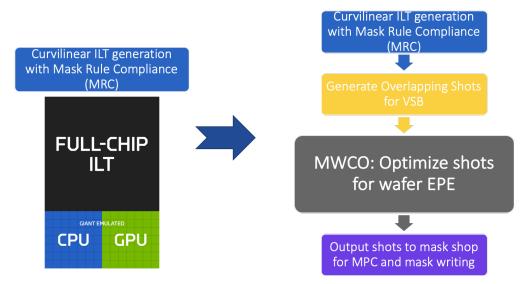

Figure 4: (a). Today, mask shape is the hand-off between OPC and Mask Shops; (b). MWCO shifts hand-off to mask shots

Today's semiconductor manufacturing process separates the responsibilities between the OPC/ILT shop and the mask shop (Figure 4 (a)). The OPC/ILT shop has the responsibility to specify the desired mask shapes in order to achieve the best wafer results. They provide the post-OPC GDS/OASIS file specifying the mask shape. The mask shop has the responsibility to manufacture the masks as close as possible to the shapes specified by OPC/ILT. The mask shop takes the GDS/OASIS file containing the mask shape, runs mask process correction (MPC) – either rule-based or model based – then fractures the mask shape into rectangles, where each rectangle is a shot that VSB mask writer writes.

Realistic limitations of mask making are codified as mask design rules that the OPC/ILT shop needs to obey when specifying mask shapes. Other realities of mask making are considered in OPC/ILT as well, most notably the consideration that VSB mask writing that is best for Manhattan (axis-parallel) rectangles with some provisions for 45-degree triangles. Since a major factor in mask cost and mask yield is mask write time, and the principle factor in mask write times (given a speed of resist dictated by the mask process for VSB-based mask writing) is the shot count, OPC/ILT tries to minimize mask shot count by various techniques, such as matching jog locations on opposite sides of a line [25].

With ILT, a Manhattanization process is explicitly invoked wherein the wafer shape is optimized given a certain minimum jog size, such as 20nm (mask dimensions), to avoid creating shapes that would take too many shots in the VSB writer [26]. But whether complex OPC or ILT, the specified mask shapes are complex, mostly rectilinear shapes with small 90-degree jogs, often with jog lengths of 20nm (mask) or less. Manufactured with mask processes that have a blur radius of 20-25nm (mask), these jogs *are understood to become curves on the mask*, often with the adjacent jogs interacting with each other. There is always a difference between the specified rectilinear shapes and the actual, curvilinear mask contours that result from that specification. Overlapping shots take advantage of this difference, using it as a tolerance in edge placement of the mask contour that can reduce shot count, while still shooting approximately the same contour, within the original EPE that the actual mask shape was going to have anyway.

In the traditional separation of responsibilities between the OPC shop and the mask shop, determining the overlapping shots that could write the mask shapes specified by the OPC shop was the domain of the mask shop. Even if error tolerances are within the original expectations, the idea that the originally specified shape is being slightly modified is disconcerting to the mask shop. Simulation-based contour checking is required, for example, because XOR checks will not pass.

MWCO marries curvilinear ILT with curvilinear mask-data preparation (MDP) for VSB writers, using overlapping shots. MWCO incorporates overlapping shot generation and mask-wafer double simulation into the ILT process, so that the output of the OPC shop is already optimized for shot count (Figure 5). By using double simulation, wafer EPE is iteratively optimized while manipulating VSB shot edges to produce rectilinear target mask shapes that are known to be writable on a VSB writer, with a known and an acceptable shot count. In the MWCO flow, the OPC shop hands off mask shots to the mask shop, instead of mask shapes (Figure 4 (b)). The mask shop will still run MPC, with its more accurate mask process models, but the mask shop does not need to fracture the mask shape – the file given by the OPC shop is a shot list that VSB mask writer can write.

Figure 5: MWCO flow for full-chip, curvilinear ILT for VSB mask writers

#### 2.4 Actual Masks are Curvilinear: Even Rectilinear Mask Design Creates Curvilinear Masks

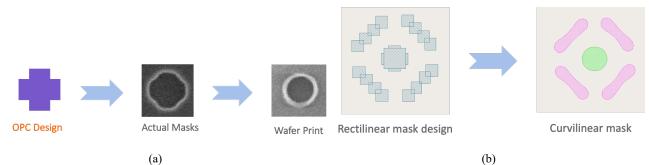

As discussed in the previous section, actual mask shapes are curvilinear, even when the specified shape is rectilinear (Figure 6(a)).

Similar to lithography and wafer process, mask writing and mask process also are subject to proximity effects. In mask writing, a number of effects including beam blur and resist blur act as low-pass filters that rounds the shapes provided on input. In particular, highly jagged shapes with many 90 degree jogs that are 20-30nm of each other will have much smoother curves than the input shapes suggest. Due to these effects, even when a designer and/or OPC engineer draw a rectilinear pattern, the result on mask will be a curvilinear mask pattern.

As shown in Figure 6 (b), the post-OPC/ILT contact main feature is a rectilinear pattern, while the simulation shows the mask pattern becomes a circular shape; the OPC/ILT design for the assist features is a rectilinear pattern with staircase jogs, while the simulation shows the mask patterns become smooth, curvy assist features on mask.

Figure 6: (a). Example of OPC design, actual mask pattern (SEM image) and wafer pattern (SEM image). (b). Example of rectilinear mask design and its simulated curvilinear mask pattern

#### 2.5 Balance Shots for Write Time and Mask-Pattern Fidelity; Main Features: Conventional, SRAFs: Overlapping

The majority of the shot count for any given mask is from curvilinear SRAFs. In our case study (detailed in section 3.2 of this paper) of a contact array with different densities, over 80% of the shots were needed to create the curvy SRAFs. Because SRAFs have relatively little impact on wafer EPE, overlapping shots can be used on SRAFs to dramatically reduce shot count. Main features, on the other hand, have a large impact on wafer EPE; therefore, conventional shots can be used for more precision, as shown in Figure 7.

Figure 7: Illustration of writing SRAFs with overlapping shots, while writing main features with conventional shots

#### 2.6 MWCO: The Key is to Minimize and Move Shots based on Wafer EPE, not Mask EPE

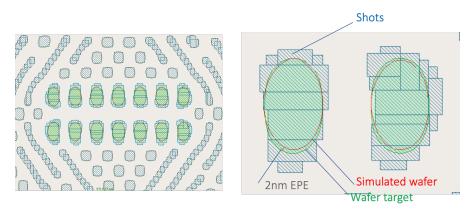

Figure 8 shows an example contact array with curvilinear ILT producing desired curvilinear mask target shapes, then VSB shots being generated for it using overlapping shots as previously published [23, 24, 27]. In the figure, green lines show the wafer target, red lines show the wafer image simulated from mask images simulated from the VSB shots in a double simulation process. The VSB shots are shown as hatched blue rectangles. Overlapping shots are used to shoot SRAFs on the mask that do not print on the wafer. For the SRAFs, thin brown lines reflect the target curvilinear mask shapes output by curvilinear ILT. Non-overlapping shots shoot the main features, but with shot count just large enough to produce the target mask contour as specified by curvilinear ILT (not shown). MDP for overlapping shots is simulation-based, with iterative optimization to produce a shot configuration that produces the desired mask contour with a low shot count, taking advantage of the natural corner-rounding in the mask process, which is especially prominent with SRAF dimensions. To the right is a zoomed-in picture of the two main features on the lower right of the contact array. Without using MWCO, the red contour of the simulated wafer image comes within 2nm EPE after mask-wafer double simulation. Because this process first produces the target curvilinear mask shapes using curvilinear ILT, and then separately optimizes the VSB shots to hit the desired mask contours, the trade-off with shot count inevitably results in accuracy loss, such as this 2nm EPE.

Figure 8: VSB shots generated to minimize mask EPE

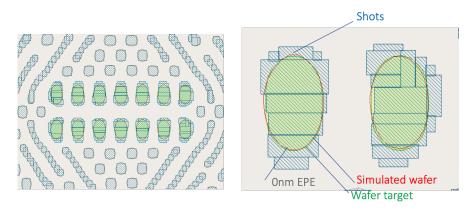

The wafer results can be much improved with MWCO. Figure 9 shows the results when the shots to produce the mask contours are moved based on mask-wafer double-simulated *wafer* EPE. By taking this approach, without changing the shot count or shot configuration much, the wafer EPE is reduced from 2nm to 0nm at the same location and less than 1nm in all the shapes. Iteratively optimizing VSB shot edges while optimizing for *wafer* EPE significantly improves the ability to target curvilinear mask shapes while minimizing impact on shot count.

Figure 9: VSB shots generated to minimize wafer EPE

#### 3. VSB MASK WRITE AND WAFER PRINT RESULTS FOR FULL-CHIP, CURVILINEAR ILT USING MWCO FOR 1931

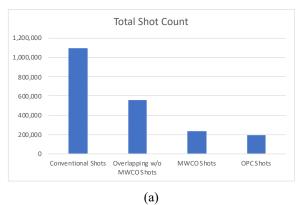

#### 3.1 Targeting Wafer, not Mask, MWCO Produces ILT with VSB Shot Counts Comparable to OPC Designs

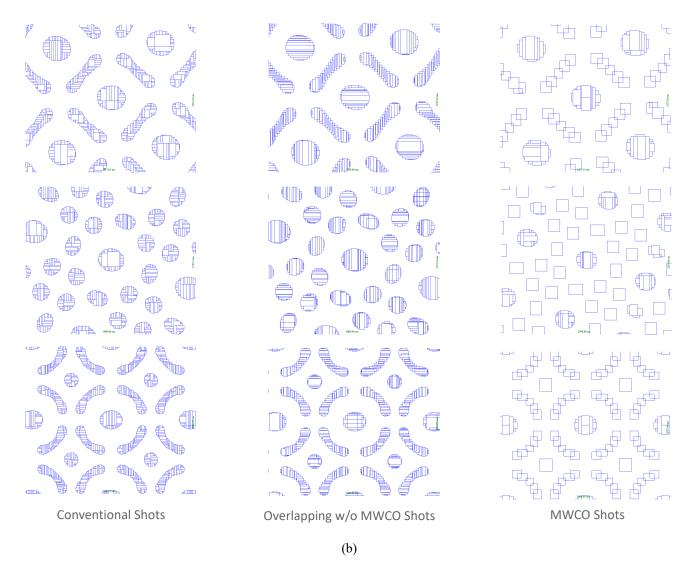

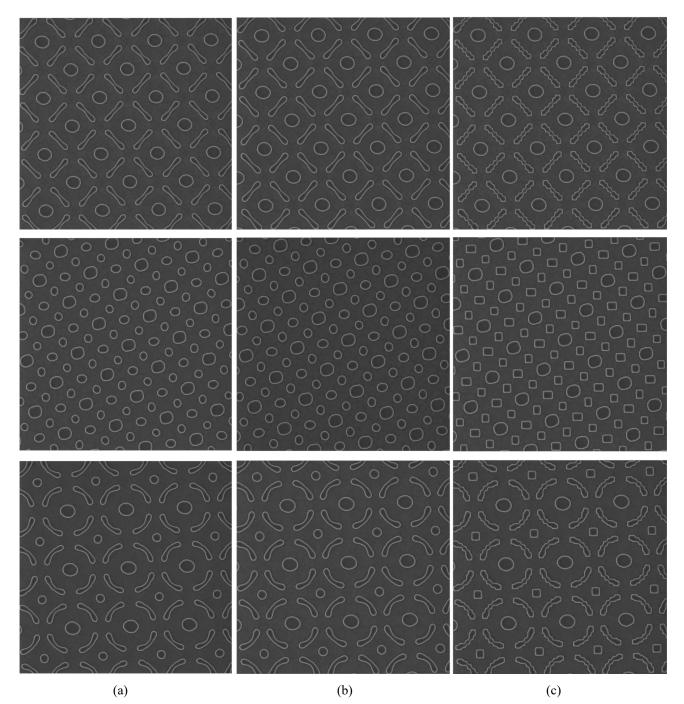

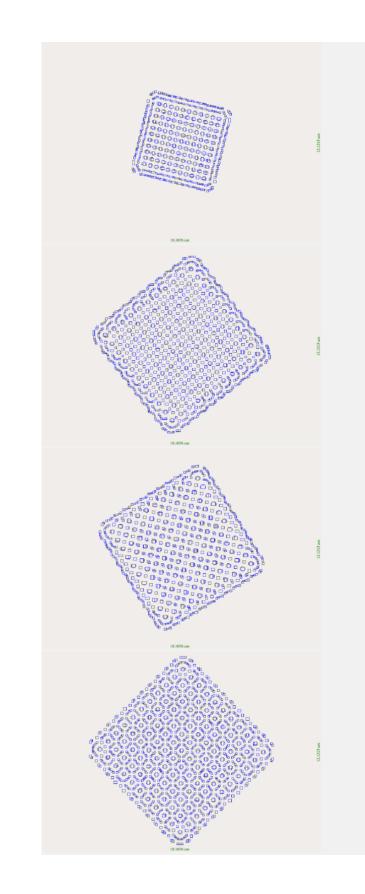

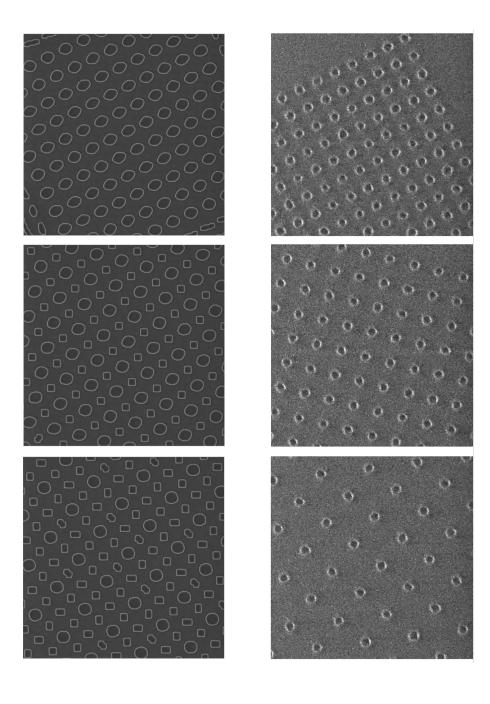

Once the optimization target is changed from mask to wafer, MWCO can further reduce the shot count, since the scanner is a band-limited optical system that will filter out high frequency features on mask. Figure 10 shows three clips for the contact array sequence that was used in our 2019 paper [20]. It has 121 different configurations of a 11 x 11 contact array, each with slightly varied pitch and rotation angle. The contact array sequence includes features in a spectrum of placements, from dense placement all the way to nearly isolated features, with the contact array rotated to demonstrate the underlying curvilinear, all-angle, nature of this solution. The total shot count when using conventional fracturing is a little over 1 million shots. Overlapping shots without MWCO reduces the shot count by roughly half to a little over half a million shots. MWCO reduces the shot count by half again, to a little less than a quarter million. The OPC shot count is about 200K, so the MWCO shot count is comparable to OPC shot count, meaning the MWCO mask has about the same write time as OPC mask.

Figure 10: (a) VSB shot count and (b) shot configurations for three contact arrays. Note the POR OPC shot configurations are not shown in (b)

The actual mask was written by Micron mask shop using the NuFlare VSB mask writer EBM-9500 PLUS. Figure 11 shows mask SEM images for the three configurations from Figure 10. One can see that the curvilinear ILT mask patterns were actually produced by the VSB mask writer. The curvilinear SRAFs in the MWCO do have staircase jogs, but since these SRAFs were made with large size overlapping shots, their dose margin is good.

#### 3.2 MWCO Enables Even a VSB Mask Writer to Write Full-Chip, Curvilinear ILT Masks in 12 hours

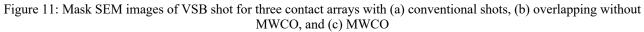

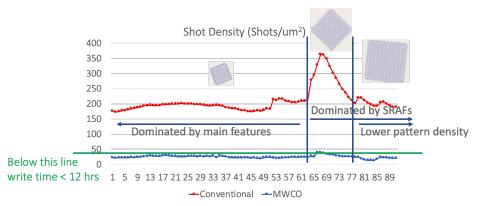

Previous works have shown that a multi-beam mask writer [28] can write a full-chip, curvilinear ILT mask in 12 hours for 193i processes[20]. The next question was, can a VSB mask writer write full-chip, curvilinear ILT masks for 193i within this same time frame? Figure 12 is a write-time comparison chart presented by NuFlare, comparing write times between their VSB writer and their multi-beam machine [29]. Because VSB mask write time is proportional to the number of shots, according to this NuFlare chart, it is only when shot count is greater than 200 Gshots/pass that VSB write times exceed 12

hours; below the 200 Gshots/pass level, VSB write times are faster than 12 hours even at 75 uC/cm<sup>2</sup>. When this number is converted into shot density per square micron, it turns out the magic number is 36 shots/um<sup>2</sup>. If the shot density is below this number, the mask write time using a VSB mask writer (i.e., NuFlare EBM 9500) will be less than 12 hours.

Figure 12: NuFlare's estimation of mask write time for their VSB mask writer and multi-beam mask writer [28]

MWCO was applied to the same contact array sequence used in the 2019 paper [20]. We applied MWCO to each pattern in the sequence to generate an overlapping VSB shot solution for each pattern. Figure 13 shows some examples in this sequence.

44  $\bigcirc$ f

Figure 13: MWCO results for contact array sequence from 2019 paper

VSB shot density for each configuration in this array sequence is computed and shown in Figure 14. Since this array sequence includes different sizes and rotations, effective areas that cover only the actual array region are used in the calculation; in other words, the empty area outside of the array is not used in the shot density calculation, and therefore does not bias the shot density. The chart shows the shot density for every configuration is below 36 shots/um<sup>2</sup>. There are three general regions in this sequence. The first region is dominated by main features. In this region, using bigger jogs/shots by using mask-wafer double-simulation is the magic behind the shot-count reduction. The second region is dominated by SRAFs. In this region, using overlapping shots on SRAFs dramatically reduces the shot count to keep shot density below 36 shots/um<sup>2</sup>. The third region is still dominated by SRAFs, but due to a larger pitch, the pattern-density is lower, making the shot density even lower than the first or second regions – well below 36 shots/um<sup>2</sup>. The chart also shows that using conventional shots (the red line) results in shot densities that are much higher, with minimum about 180 shots/um<sup>2</sup>, which translates to about 5X the write time. For the second region, due to curvilinear SRAFs, the write time for conventional shots skyrockets, to 10X.

Figure 14: VSB shot density of MWCO results for the contact array sequence from Figure 11

#### 3.3 Curvilinear ILT Mask and Corresponding Wafer Results Using MWCO

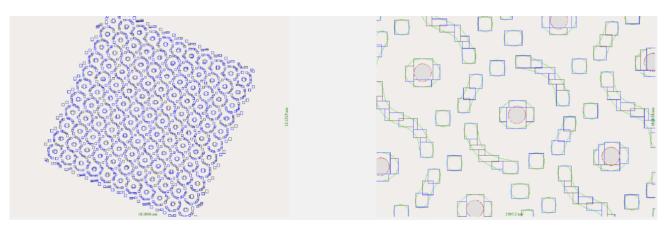

Figure 15 shows SEM images of curvilinear ILT mask and its corresponding wafer print for the same contact array used in previous sections. The contact ADI target is 40nm, and the minimum pitch is 100nm. One can see that the contact array was printed nicely with this MWCO curvilinear ILT mask: the contact holes are printed evenly across all the varied pitches and rotations, as well as from the center of the array all the way to the edge of the array, which is very challenging for OPC.

(a)

(b)

Figure 15: MWCO results for the same contact array used in the 2019 paper. In each pair, on the left (a) are MWCO VSB mask SEM images of curvilinear mask designs for different pitches and orientations; on the right (b) are SEM images of corresponding wafer print

#### 3.4 MWCO Produces 2X Process Windows than OPC

The 2019 paper demonstrated that curvilinear ILT (in that case, written with a multi-beam mask writer) produces the largest process window. We have already seen that MWCO reduces the shot count and mask write time by 4X on VSB mask writer, as compared to conventional shots. Does ILT with MWCO written by a VSB writer produce similar process window enlargement benefits?

Proc. of SPIE Vol. 11518 115180W-14

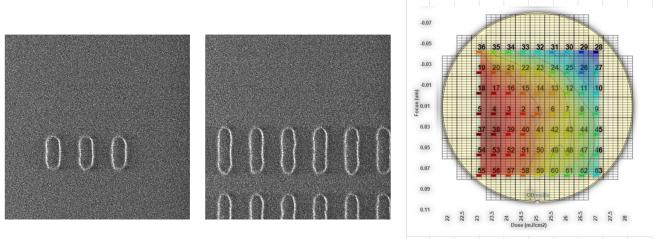

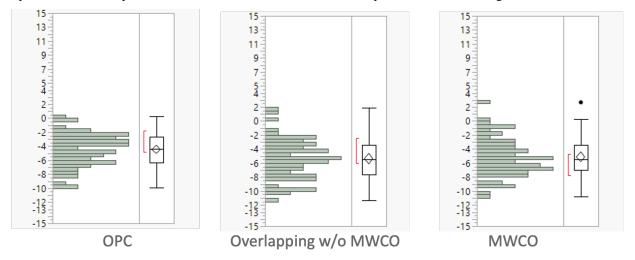

For this study, 61 different patterns – including some of the most challenging ones found in lithography and OPC – were selected. They were treated with conventional OPC VSB shots, Curvilinear ILT using overlapping VSB shots without MWCO, and overlapping VSB shots with MWCO. All of the patterns were written on the same mask using the NuFlare VSB mask writer EBM-9500 PLUS. The wafer was printed at seven different focuses and nine doses, for a total of 63 different process conditions (Figure 16).

Sample wafer prints for CD measurements

Figure 16: Wafer process window study to compare curvilinear ILT produced with different VSB options and OPC

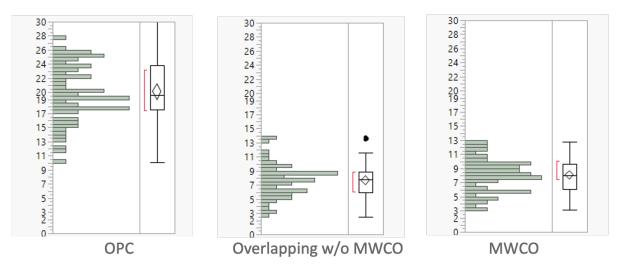

Figure 17 shows the distribution of mean-to-target value for all measurement sites at the nominal condition. One can see the bias for conventional OPC, curvilinear ILT with overlapping shots without MWCO, and curvilinear ILT with overlapping shots with MWCO are all around -5nm. The CD variation distributions for three cases are also about the same. This provides a fair comparison basis when we look at variations when process condition changes.

Figure 17: CD mean-to-target variations for all 61 test patterns/site at the nominal condition for OPC, Curvilinear ILT using overlapping shots without MWCO, and MWCO

Figure 18 is the CD variation distribution for all 63 process conditions. Instead of plotting mean-to-target as in Figure 17, here maximum CD minus minimum CD for all process variations for each pattern and measurement site is used, that is why the numbers are all positive. It is very clear that curvilinear ILT using overlapping shots without MWCO and curvilinear ILT using overlapping shots with MWCO reduces the CD average variation by about 3X, from 20nm to 7nm. In addition, the CD variation spread is also narrowed by half.

Figure 18: CD maximum minus minimum variations within all 63 process conditions for all 61 test patterns/site for OPC, Curvilinear ILT using overlapping shots without MWCO, and MWCO

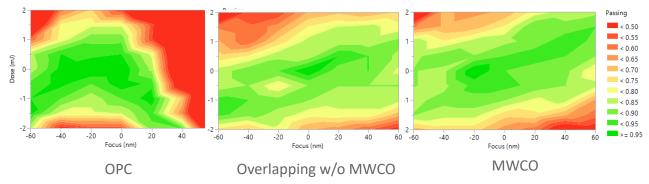

Figure 19 is the process window plot. The x-axis is the focus, the y-axis is the dose change. Since there are 61 sites, we plot the ratio of the number of sites meeting the process window requirement to the total number of sites. A CD variation of 10% is used as the process window criteria. The pseudo color from green to red represents process window from good to bad. Overall curvilinear ILT using overlapping shots without MWCO and curvilinear ILT using overlapping shots with MWCO greatly enlarged the green (or non-red) region by over 2X, especially the depth of focus. Comparing overlapping without MWCO and with MWCO, the MWCO is slightly better, showing the benefit of optimizing wafer EPE instead of mask EPE while only using half number of shots as the overlapping shots without MWCO case.

Figure 19: Process window plots for all 61 test patterns/sites at the all 63 process conditions for OPC, Curvilinear ILT with overlapping shots without MWCO, and curvilinear ILT using overlapping shots with MWCO

#### 4. SUMMARY AND CONCLUSIONS

#### ILT Vision Realized: Full-Chip Curvilinear ILT with Full Mask VSB Writing in 12 hours for 193i

For more than a decade, the semiconductor industry has recognized the value of ILT in addressing the challenges of advanced-node lithography. Until now, runtime and VSB write-times have been insurmountable barriers to using ILT as a full-chip solution. By embracing a unique, holistically conceived, purpose-built system of GPU-accelerated hardware and software that emulates a single giant GPU/CPU pair, stitchless, curvilinear, full-chip ILT in a day is now a practical reality as demonstrated in the 2019 paper.

Mask-wafer co-optimization (MWCO) is now introduced as a further enhancement, combining overlapping shots with mask and wafer double-simulation to demonstrate that curvilinear ILT for 193i is practical with VSB mask writers.

Extensive mask and wafer experiments were performed to study curvilinear ILT using conventional shots, overlapping shots with MWCO, and OPC to produce patterns commonly seen in memory applications. Tens of thousands of mask and wafer SEM images and CD measurements were collected and analyzed. The mask data showed overlapping shots without MWCO and with MWCO can enable a VSB mask writer to produce accurate curvilinear ILT masks. The mask write time using overlapping shots without MWCO is comparable to conventional OPC. The wafer results for both curvilinear ILT using overlapping shots without MWCO and with MWCO and with MWCO reduced CD variation by 3X over OPC at all process variations, and enlarged the process window by 2X over conventional OPC. MWCO has slightly better process window than overlapping without MWCO, but with only half of the shot count or mask write time. These results demonstrate that by employing MWCO, VSB writers can write a curvilinear ILT mask with 36 shots/um<sup>2</sup>, which, for resist sensitivities expected for 193i masks, should be below 12 hours in write time.

#### 5. REFERENCES

- <sup>[1]</sup> B.E.A. Saleh and S.I. Sayegh, "Reductions of errors of microphotographic reproductions by optical corrections of original masks", Optical Eng. Vol. 20 pp 781-784 (1981)

- <sup>[2]</sup> K.M. Nashold and B.E.A. Saleh, "Image construction through diffraction-limited high-contrast imaging systems: an iterative approach", J. Opt. Soc. Am.A, vol. 2 p. 635 (1985)

- <sup>[3]</sup> Y. Liu and A. Zachor, "Optimal binary image design for optical lithography", Proc. SPIE Vol. 1264 pp 410-412 (1990)

- [4] Y. Liu and A. Zachor, "Binary and phase-shifting image design for optical lithography", Proc. SPIE Vol. 1463 pp 382-399 (1991)

- [5] A. Rosenbluth et. al, "Optimum mask and source patterns to print a given shape", JM3 vol. 1 pp 13-30 (2002)

- <sup>[6]</sup> Y-T Wang, Y.C. Pati, H. Watanabe and T. Kailath, "Automated design of halftoned double-exposure phase-shifting masks", Proc. SPIE Vol. 2440 pp 290-301 (1995)

- <sup>[7]</sup> Y.H. Oh, and J-C Lee, Resolution enhancement through optical proximity correction and stepper parameter optimization for 0.12-um mask pattern, Proc. SPIE Vol. 3679 pp 607-613 (1999)

- <sup>[8]</sup> T. Fuhner and A. Erdmann, "Improved mask and source representations for automatic optimization of lithographic process conditions using a genetic algorithm", Proc. SPIE Vol. 5754 pp 415-426 (2005)

- <sup>[9]</sup> Abrams, Daniel S., and Linyong Pang. "Fast inverse lithography technology." In *Optical Microlithography XIX*, vol. 6154, p. 61541J. International Society for Optics and Photonics, 2006.

- [10] Pang, Linyong, Yong Liu, and Dan Abrams. "Inverse lithography technology (ILT): What is the impact to the photomask industry?." In *Photomask and Next-Generation Lithography Mask Technology XIII*, vol. 6283, p. 62830X. International Society for Optics and Photonics, 2006.

- [11] Liu, Yong, Dan Abrams, Linyong Pang, and Andrew Moore. "Inverse lithography technology principles in practice: Unintuitive patterns." In 25th Annual BACUS Symposium on Photomask Technology, vol. 5992, p. 599231. International Society for Optics and Photonics, 2005.

- [12] Lin, Benjamin, Ming Feng Shieh, Jie-wei Sun, Jonathan Ho, Yan Wang, Xin Wu, Wolfgang Leitermann et al. "Inverse lithography technology at chip scale." In *Optical Microlithography XIX*, vol. 6154, p. 615414. International Society for Optics and Photonics, 2006.

- <sup>[13]</sup> Hung, Chi-Yuan, Bin Zhang, Eric Guo, Linyong Pang, Yong Liu, Kechang Wang, and Grace Dai. "Pushing the lithography limit: Applying inverse lithography technology (ILT) at the 65nm generation." In *Optical Microlithography XIX*, vol. 6154, p. 61541M. International Society for Optics and Photonics, 2006.

- [14] Ho, Jonathan, Yan Wang, Xin Wu, Wolfgang Leitermann, Benjamin Lin, Ming Feng Shieh, Jie-wei Sun et al. "Realworld impacts of inverse lithography technology." In 25th Annual BACUS Symposium on Photomask Technology, vol. 5992, p. 59921Z. International Society for Optics and Photonics, 2005.

- [15] Moore, Andrew, Timothy Lin, Yong Liu, Gordon Russell, Linyong Pang, and Daniel Abrams. "Inverse lithography technology at low k1: Placement and accuracy of assist features." In *Photomask Technology 2006*, vol. 6349, p. 63494T. International Society for Optics and Photonics, 2006.

- <sup>[16]</sup> Hung, Chi-Yuan, Bin Zhang, Deming Tang, Eric Guo, Linyong Pang, Yong Liu, Andrew Moore, and Kechang Wang.

"First 65nm tape-out using inverse lithography technology (ILT)." In 25th Annual BACUS Symposium on Photomask Technology, vol. 5992, p. 59921U. International Society for Optics and Photonics, 2005.

- [17] Chu, Chih-Wei, Becky Tsao, Karl Chiou, Snow Lee, Jerry Huang, Yong Liu, Timothy Lin, Andrew Moore, and Linyong Pang. "Enhancing DRAM printing process window by using inverse lithography technology (ILT)." In *Optical Microlithography XIX*, vol. 6154, p. 61543O. International Society for Optics and Photonics, 2006.

- <sup>[18]</sup> Kim, Byung-Gook, Sung Soo Suh, Byung-Sung Kim, Sang-Gyun Woo, Han-Ku Cho, Vikram Tolani, Grace Dai et al. "Trade-off between inverse lithography mask complexity and lithographic performance." In *Photomask and Next-Generation Lithography Mask Technology XVI*, vol. 7379, p. 73791M. International Society for Optics and Photonics, 2009.

- <sup>[19]</sup> 2018 eBeam Initiative Perceptions Survey Results [September 18, 2018], <u>http://www.ebeam.org</u>

- <sup>[20]</sup> Pang, Linyong, et al. "Study of mask and wafer co-design that utilizes a new extreme SIMD approach to computing in memory manufacturing: full-chip curvilinear ILT in a day." *Photomask Technology 2019*. Vol. 11148. International Society for Optics and Photonics, 2019.

- <sup>[21]</sup> Russell, Ezequiel, "ILT and Curvilinear Mask Designs for Advanced Memory Designs", presented at SPIE eBeam lunch, February 25, 2020, <u>http://www.ebeam.org</u>

- <sup>[22]</sup> Pang, Linyong Leo, P. Jeffrey Ungar, Ali Bouaricha, Lu Sha, Michael Pomerantsev, Mariusz Niewczas, Kechang Wang, Bo Su, Ryan Pearman, and Aki Fujimura. "TrueMask ILT MWCO: full-chip curvilinear ILT in a day and full mask multi-beam and VSB writing in 12 hrs for 193i." In *Optical Microlithography XXXIII*, vol. 11327, p. 113270K. International Society for Optics and Photonics, 2020.

- [23] Aki Fujimura, David Kim, Tadashi Komagata, Yasutoshi Nakagawa, Vikram Tolani, Tom Cecil, "Best depth of focus on 22-nm logic wafers with less shot count," Proc. SPIE 7748, Photomask and Next-Generation Lithography Mask Technology XVII, 77480V (26 May 2010);https://doi.org/10.1117/12.866413

- <sup>[24]</sup> Zable, H., et al, "Writing Wavy Metal 1 Shapes on 22-nm Logic Wafers with Less Shot Count", Proc. SPIE 7748, 77480X (2010).

- <sup>[25]</sup> Linyong Pang, Yong Liu, Thuc Dam, Kresimir Mihic, Thomas Cecil, Dan Abrams, "Inverse lithography technology (ILT): keep the balance between SRAF and MRC at 45 and 32 nm," Proc. SPIE 6730, Photomask Technology 2007, 673052 (30 October 2007);<u>https://doi.org/10.1117/12.754568</u>

- <sup>[26]</sup> Linyong Pang, Nader Shamma, Paul Rissman, Dan Abrams, "Laser and e-beam mask-to-silicon with inverse lithography technology," Proc. SPIE 5992, 25th Annual BACUS Symposium on Photomask Technology, 599221 (7 November 2005); <u>https://doi.org/10.1117/12.632738</u>

- [27] Pang, Linyong, et al. "Model-based MPC enables curvilinear ILT using either VSB or multi-beam mask writers." *Photomask Japan 2017: XXIV Symposium on Photomask and Next-Generation Lithography Mask Technology.* Vol. 10454. International Society for Optics and Photonics, 2017.

- [28] Christof Klein, Elmar Platzgummer, "MBMW-101: World's 1st high-throughput multi-beam mask writer," Proc. SPIE 9985, Photomask Technology 2016, 998505 (25 October 2016); <u>https://doi.org/10.1117/12.2243638</u>

- <sup>[29]</sup> Matsumoto, Hiroshi, et al. "Multi-beam mask writer MBM-1000 and its application field." *Photomask Japan 2016: XXIII Symposium on Photomask and Next-Generation Lithography Mask Technology*. Vol. 9984. International Society for Optics and Photonics, 2016.