#### September 2022 | Aki Fujimura, CEO D2S, Inc.

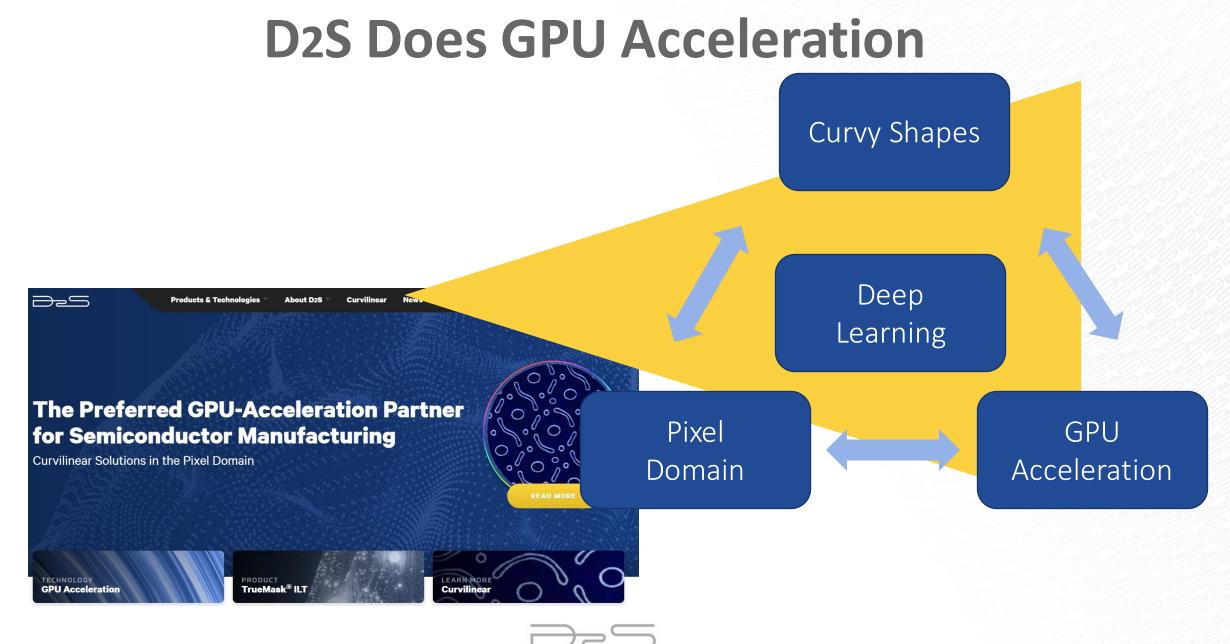

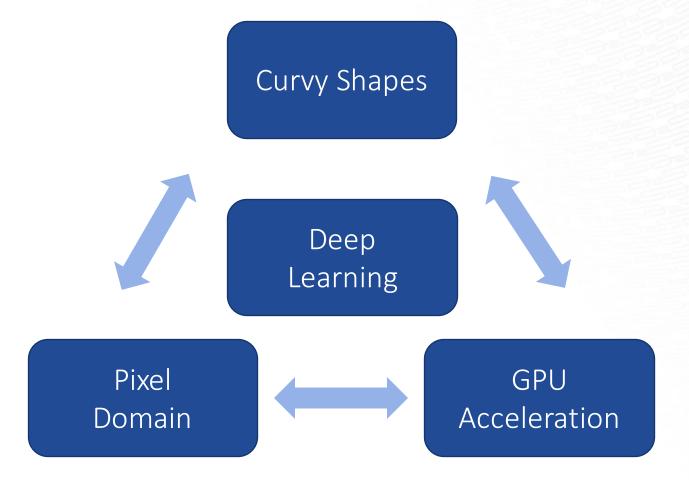

# O(p): GPUs, Pixels, DL, Curvy Masks & Designs

D2S PATENTED TECHNOLOGY. Copyright 2018-2022 D2S, Inc. D2S<sup>®</sup> and TrueMask<sup>®</sup> are US-registered trademarks of D2S, Inc. in US. TrueMask<sup>®</sup> and TrueModel<sup>®</sup> are registered trademarks of D2S, Inc. in US, Japan, Korea, China and Taiwan.

D<sub>2</sub>S PATENTED TECHNOLOGY COPYRIGHT 2018-2022 D<sub>2</sub>S, Inc.

# **GPU Accelerates Edge Manipulation, Too**

D<sub>2</sub>S PATENTED TECHNOLOGY COPYRIGHT 2018-2022 D<sub>2</sub>S, Inc.

## **GPU is Great for Curvy**

**Because GPU is even better at pixels**

D<sub>2</sub>S PATENTED TECHNOLOGY COPYRIGHT 2018-2022 D<sub>2</sub>S, Inc.

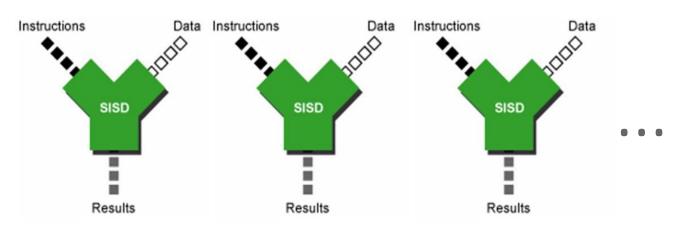

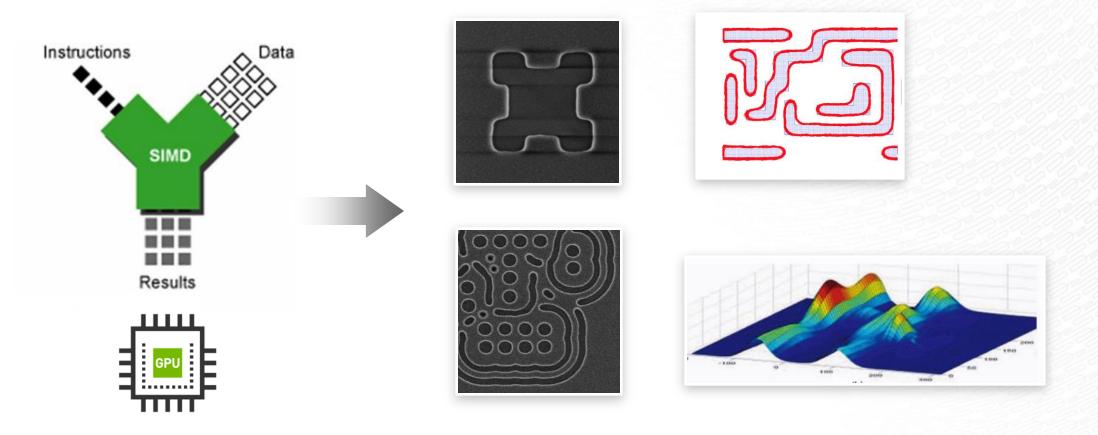

## **GPU is SIMD and SIMD is Great at Pixels**

Multiple Single Instruction Single Data (SISD)

Data

Instructions

Single Instruction Multiple Data (SIMD)

D<sub>2</sub>S PATENTED TECHNOLOGY COPYRIGHT 2018-2022 D<sub>2</sub>S, Inc.

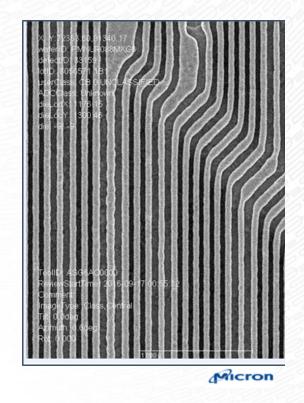

### Mask and Wafer Effects are SIMD

#### **Because nature is SIMD**

# Image Processing is SIMD, Too

Source: NuFlare/CDLe

SEM

Source: Lasertec/BACUS Newsletter

Inspection

Source: L Pang, et al., "Expanding the applications of computational lithography and inspection (CLI) in mask inspection, metrology, review, and repair"

### **Because Images are Arrays of Pixels**

D<sub>2</sub>S PATENTED TECHNOLOGY COPYRIGHT 2018-2022 D<sub>2</sub>S, Inc.

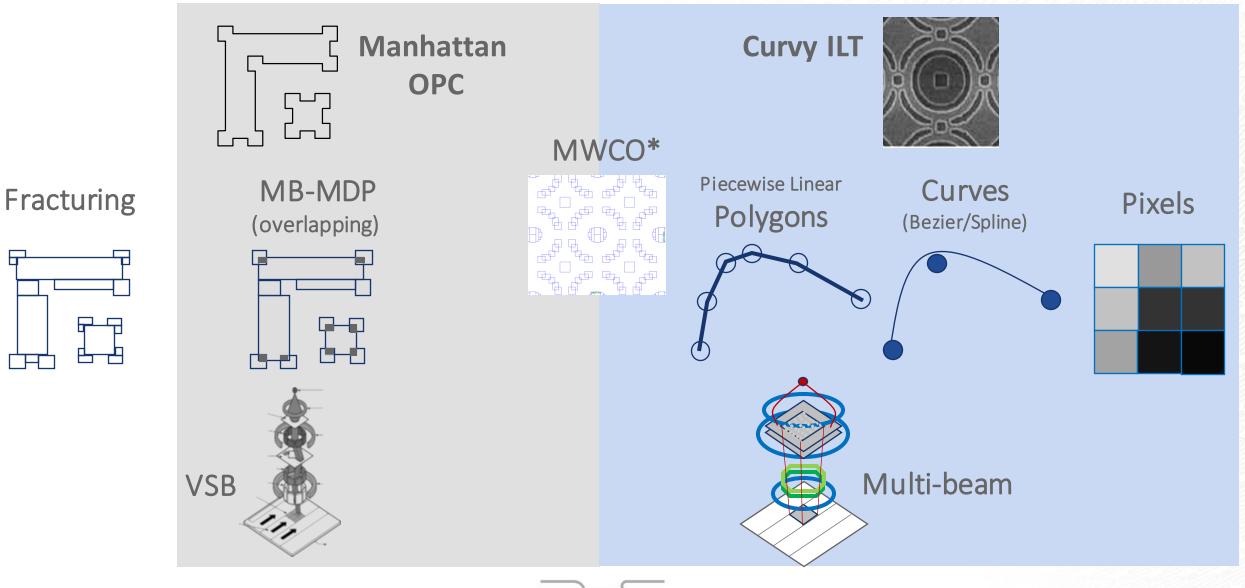

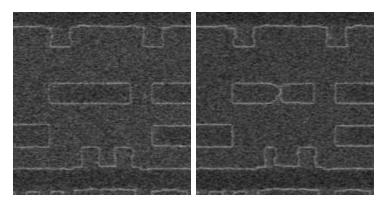

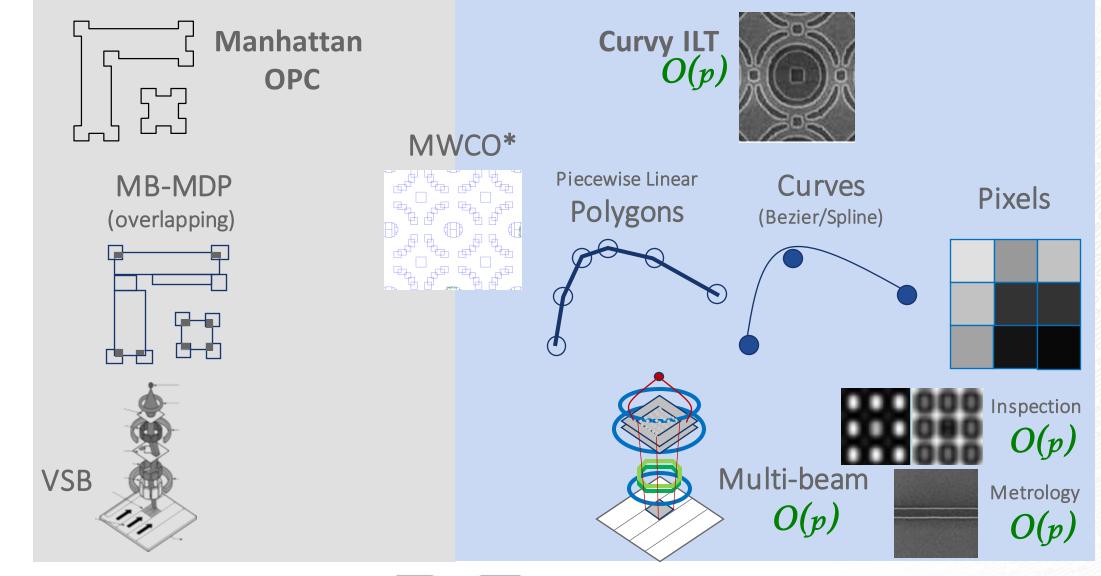

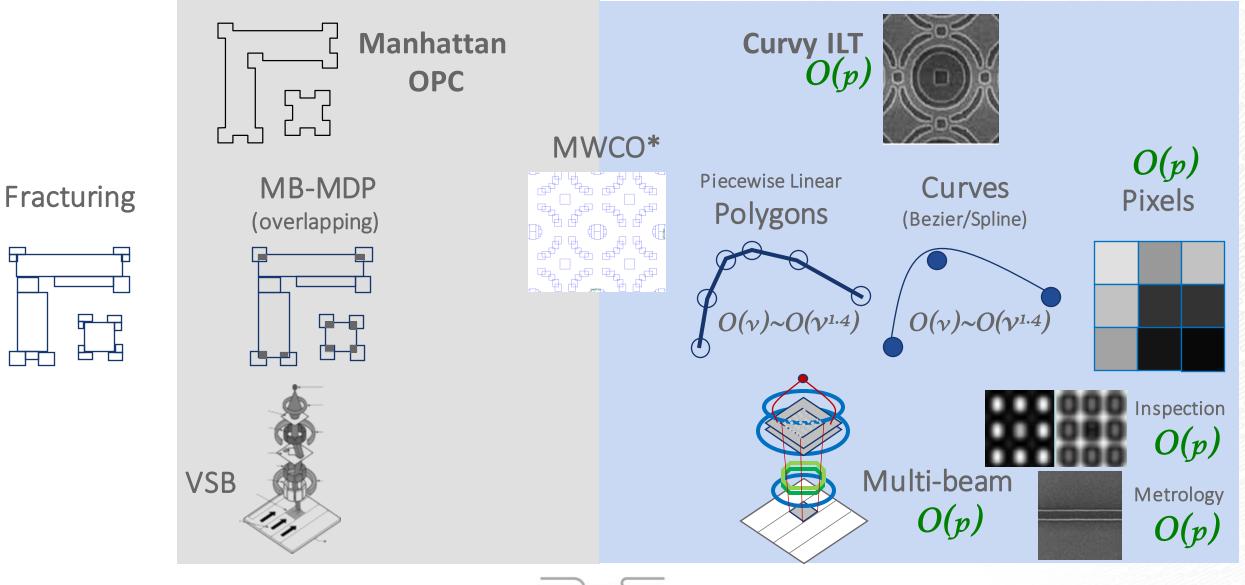

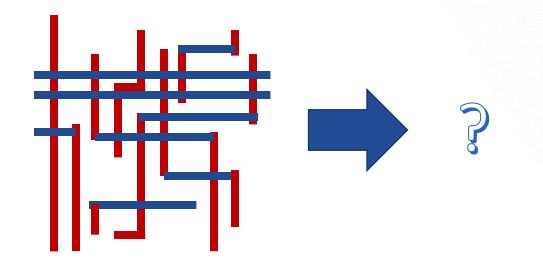

# **Pixel-Based and Edge-Based are Duals**

- Whatever you can do in one can be done in the other...given a resolution limit determined by "Nyquist"

- The only question is performance....

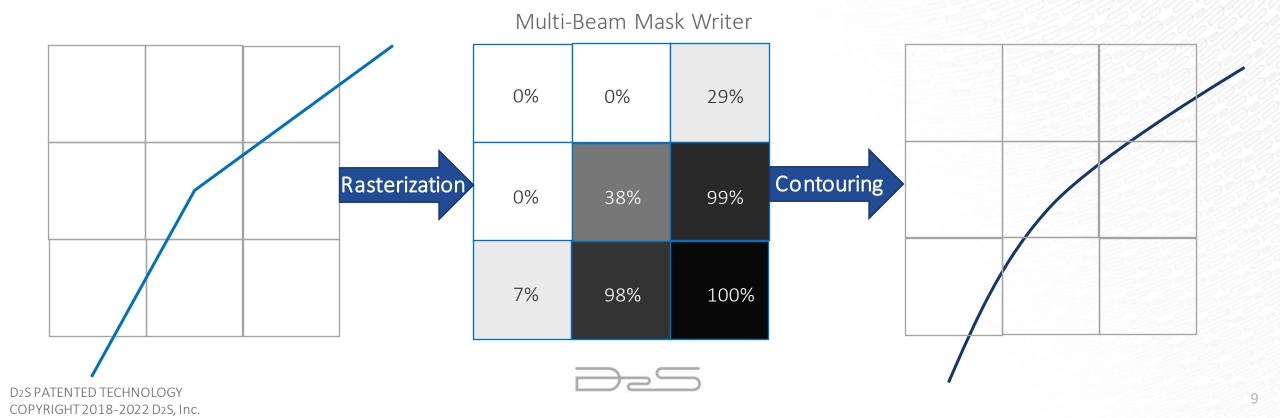

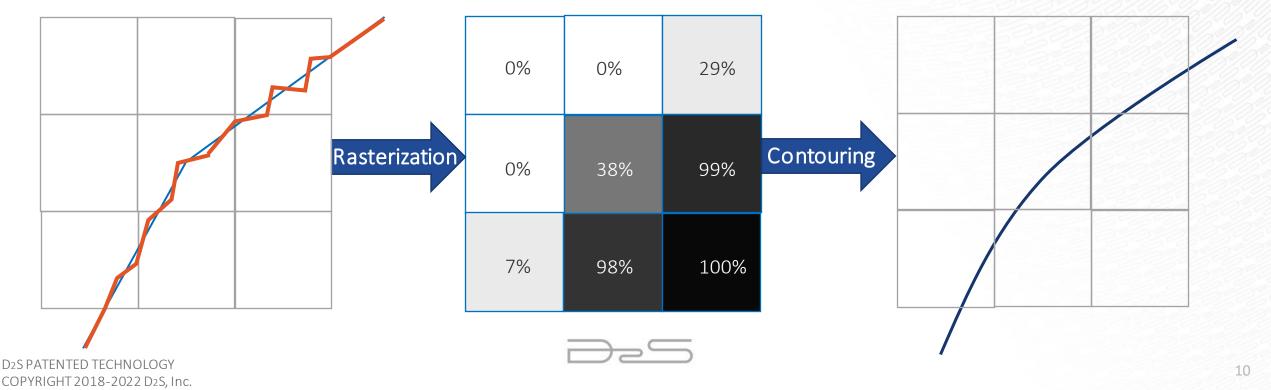

# This Also Rasterizes Exactly the Same

- Rasterization is inherently a low-pass filter

- Red and blue become the same in pixels, but red uses much more data

- Curvilinear format would also become the same in pixels and thereafter

- And represents the actual contoured shape that would be on the physical mask

# Mask-Making is Already Pixel-Based

D<sub>2</sub>S PATENTED TECHNOLOGY COPYRIGHT 2018-2022 D<sub>2</sub>S, Inc.

Fracturing

# **Datapath is Not**

# D2S is Adding a Pixel-Based Datapath

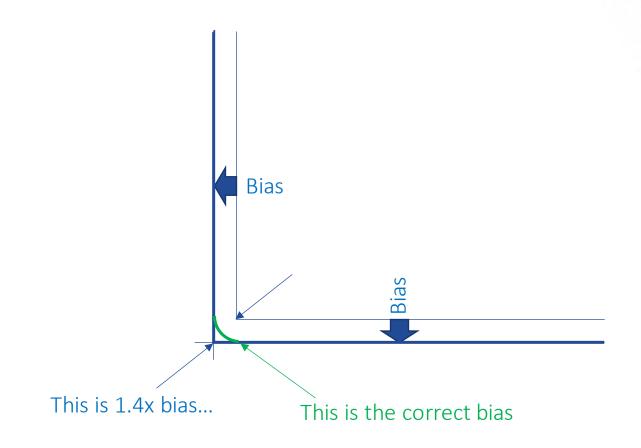

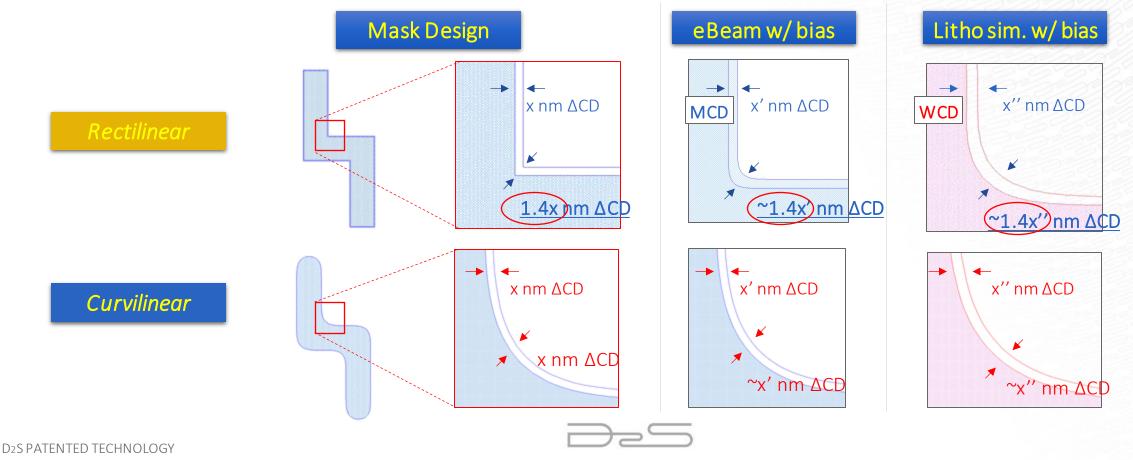

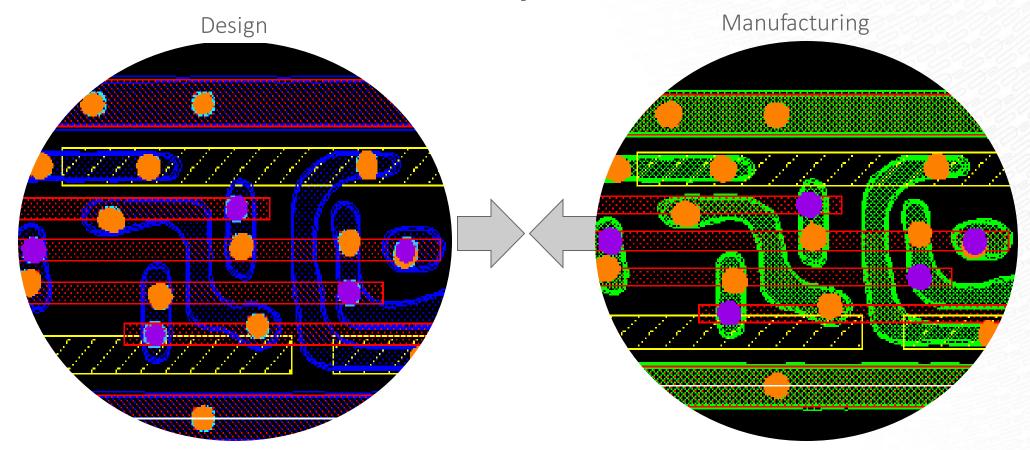

### Edge or Pixel, Curvy Improves Manufacturing Simple example : Biasing

For traditional Manhattan edge-based CAD, it is bad to have bias create curvy shapes. So this is understandable but incorrect. Etching, for example, doesn't work that way.

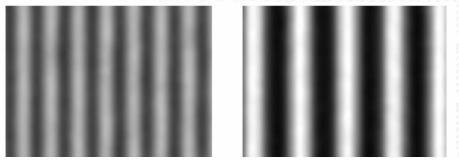

# **Even a Simple Bias Operation is Better with Curvy**

### Rectilinear bias is off by 40% on corners

COPYRIGHT 2018-2022 D<sub>2</sub>S, Inc.

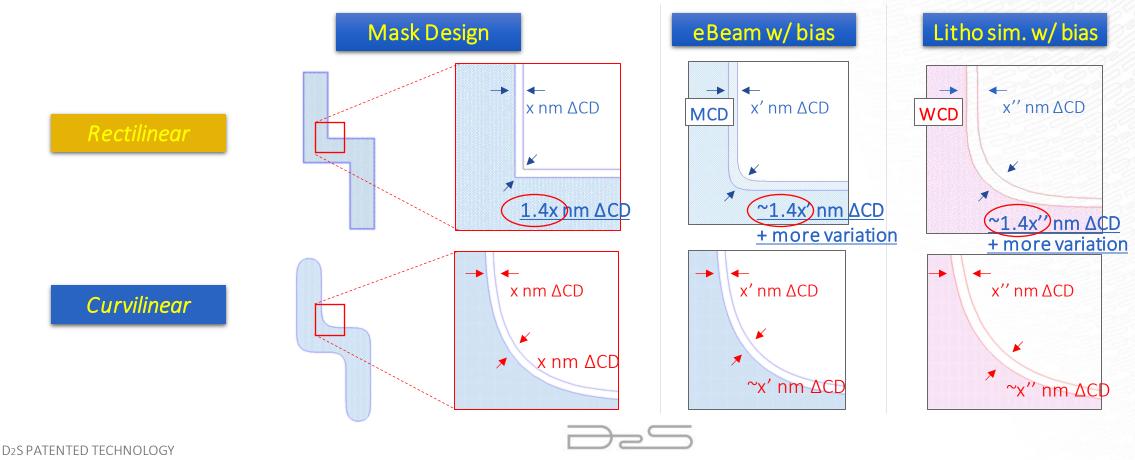

# **Even Worse is Manufacturing Variation**

### Dose margin is bad on 90° corners

COPYRIGHT 2018-2022 D<sub>2</sub>S, Inc.

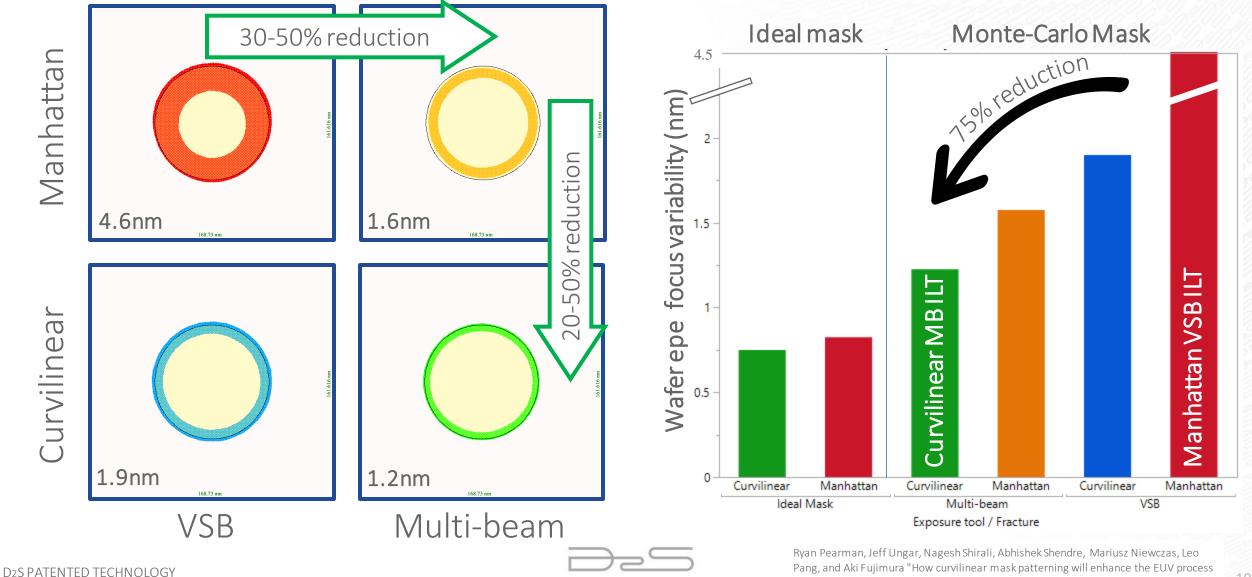

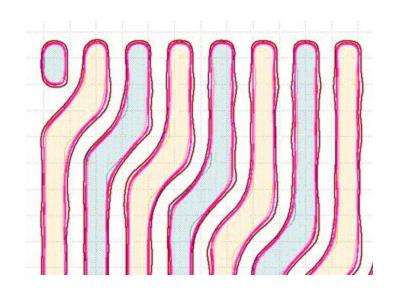

# <sup> Beam</sup> Manufacturable Shapes are More Reliably Manufacturable

COPYRIGHT 2018-2022 D<sub>2</sub>S, Inc.

Pang, and Aki Fujimura "How curvilinear mask patterning will enhance the EUV process 19 window: a study using rigorous wafer+mask dual simulation", Proc. SPIE 11178, (2019)

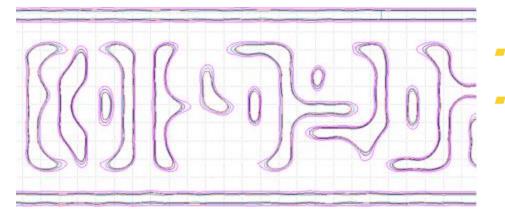

### Manufacturable Shapes are More Reliably Manufacturable

On Wafer, too

### First thing ILT does is to compute manufacturable curvy targets anyway

## I Presented This at Design Automation Conference

"I was in EDA physical design since 1979 so I know it's important for you to know: Curvilinear Designs are Now Manufacturable. In fact, More Reliably Manufacturable."

## Is it Time to Break the Manhattan Assumption?

#### Most chips are interconnect-limited; Reducing vias will reduce routing congestion

| D2S PATENTE DITECHINO GOGY  |

|-----------------------------|

| CONFYREGHT 2018-2022 DESARC |

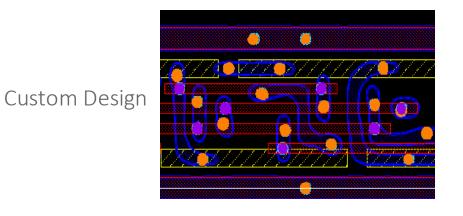

# **Curvy Designs are Better for Designers, Too**

- Manufacturable Curvy Designs

- Improves, all at the same time

- Yield

- Power

- Performance

- Area

- The barriers are:

- VSB mask writing

- EDA infrastructure

Actually: Only Routing plus Performance Improvements

Routing

Parasitic Extraction

# Curvy-Pixel-GPU Can Work for Them, Too

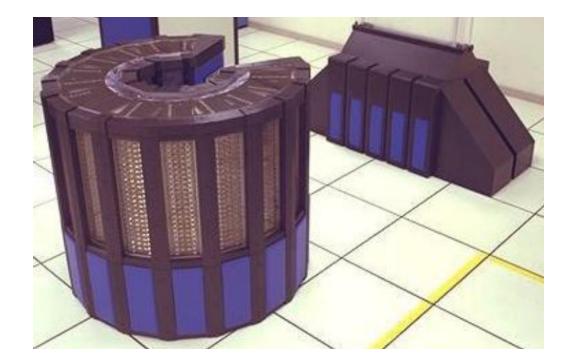

## Today's GPU Workstation = 8,000 Cray-2s

60,000,000x Price Performance It's time to rethink EDA

#### Cray-2 (1985) 1.9 GFLOPS w/500MB @ \$15M

nVIDIA RTX 3090 Ti (2021) 15,300 GFLOPS w/24GB @ \$2,000

### 16,000? Today's GPU Workstation = 8,000 Cray-2s

150,000,000x? 60,000,000x Price Performance It's definitely time to rethink EDA

#### Announced Last Tuesday

#### Cray-2 (1985) 1.9 GFLOPS w/500MB @ \$15M