# Why is Curvy Design an Opportunity Now?

Moderator:

Panel:

Aki Fujimura, CEO, D2S, Inc.

John Kibarian, CEO, PDF Solutions Ezequiel Russell, Sr. Director of Mask Technology, Micron Andrew Kahng, Professor, UCSD Steve Teig, CEO, Perceive 01010 10401 41m

â

### San Francisco is Ahead of the Curve

#### **Today's GPU Workstation = 43,000 Cray-2s** 340,000,000x Price Performance: It's time to rethink EDA

RTX 4090

Cray-2 (1985) 1.9 GFLOPS w/500MB @ \$15M

NVIDIA RTX 4090 (2022) 83 TFLOPS w/24GB @ \$1,900

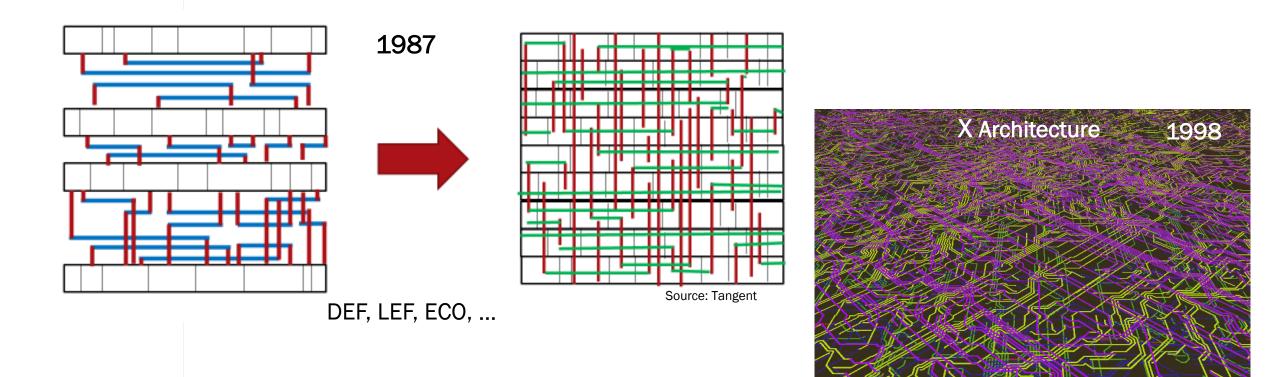

#### Once Upon a Time, Rectangles Served a Purpose But times (and computing) have changed...

Source: Shore .

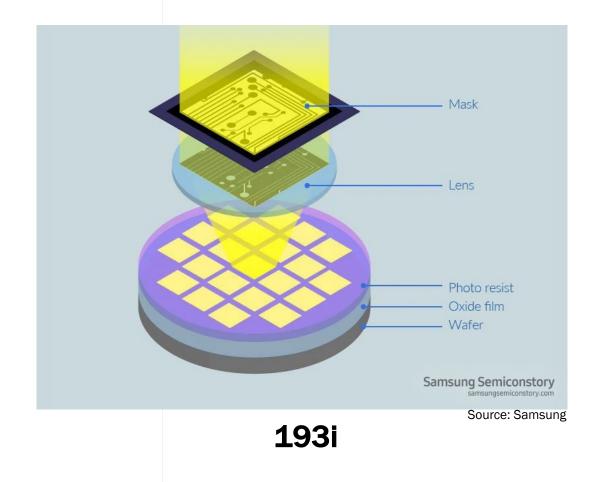

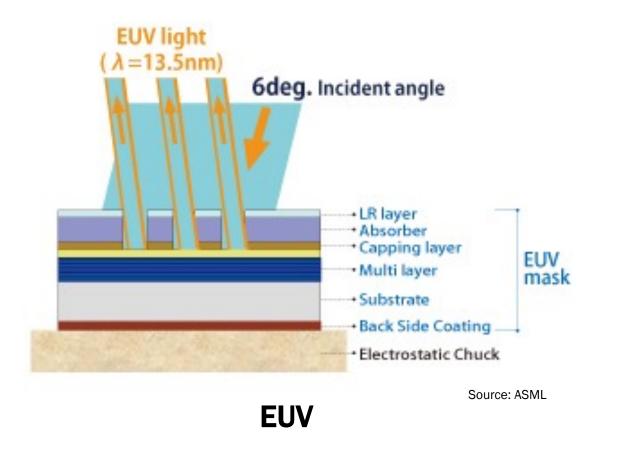

#### Wafers are Exposed by Masks (EUV, too!)

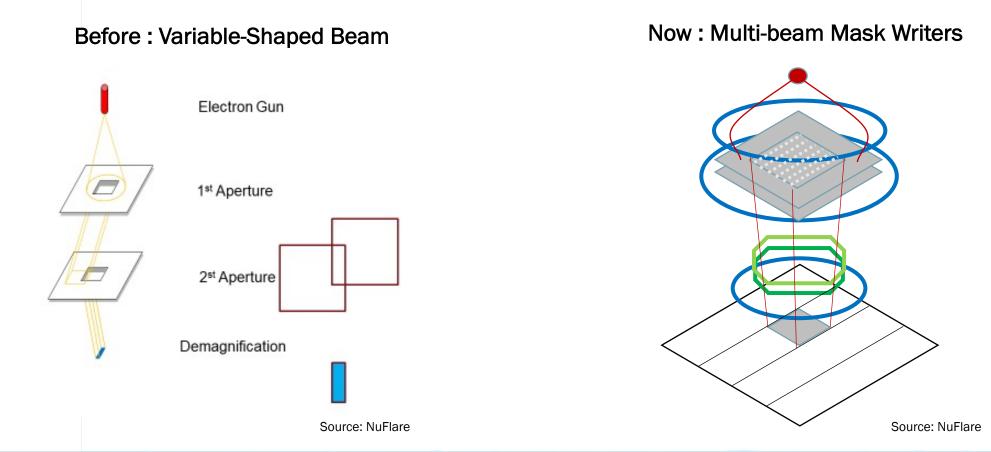

#### Leading Edge is 100% Multi-beam Mask Writers Multi-beam write-time is independent of shape: Curvilinear (curvy) masks have been enabled

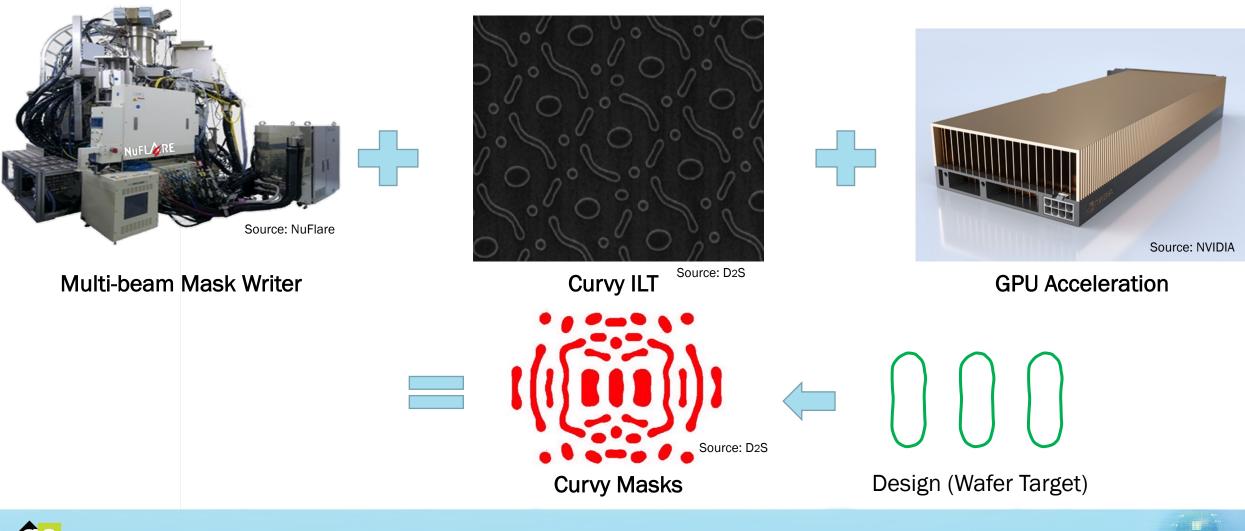

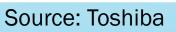

#### ILT is Software that Computes Mask Shapes Generates Curvy Masks for Multi-beam Writing

Design (Wafer Target)

Curvilinear ILT (Mask Target)

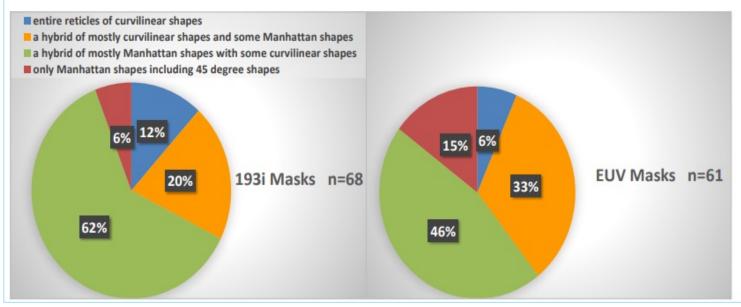

### Both 193i and EUV Will Use Curvy Masks

• Masks are written by data • Wafers are written by masks • Before: Manhattan Some 45-degree triangles Now: Curvy Masks Just as accurately Just as quickly • For the same cost

Manufacturing of curvilinear masks is enabled by multi-beam mask writers. How extensively will curvilinear shapes be used for leading-edge (EUV, 193i) masks intended for high volume manufacturing (HVM) by 2023?

eBeam Initiative Luminaries Survey, ebeam.org

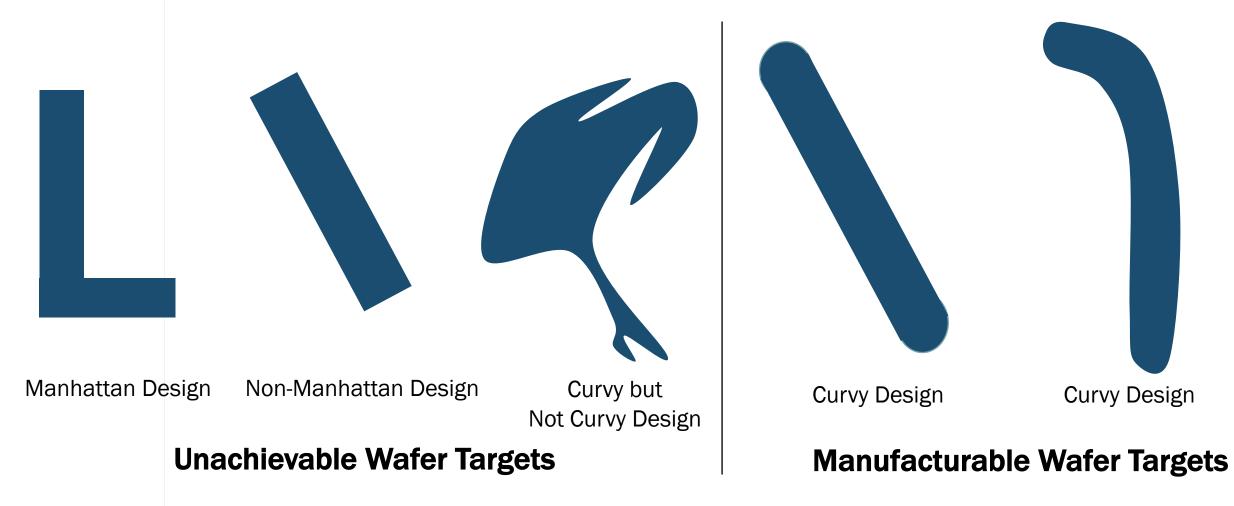

### **Curvy Wafer Targets Can Be Manufactured Now**

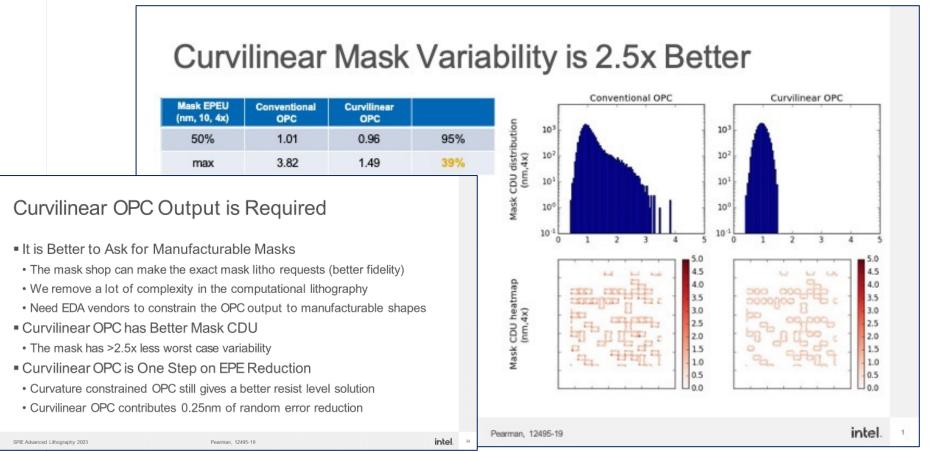

## "Ask for what you want!" - Ryan Pearman, Intel

#### **True for Wafer Targets too!**

Source: Pearman, et al, Intel, "A CD Uniformity study comparing MRC-constrained Manhattan to Curvilinear OPC corrections on EUV", SPIE AL 2023, 12495-19

#### "Curvy Design" Means Curvy Connections Manufacturable Shapes are More Reliable

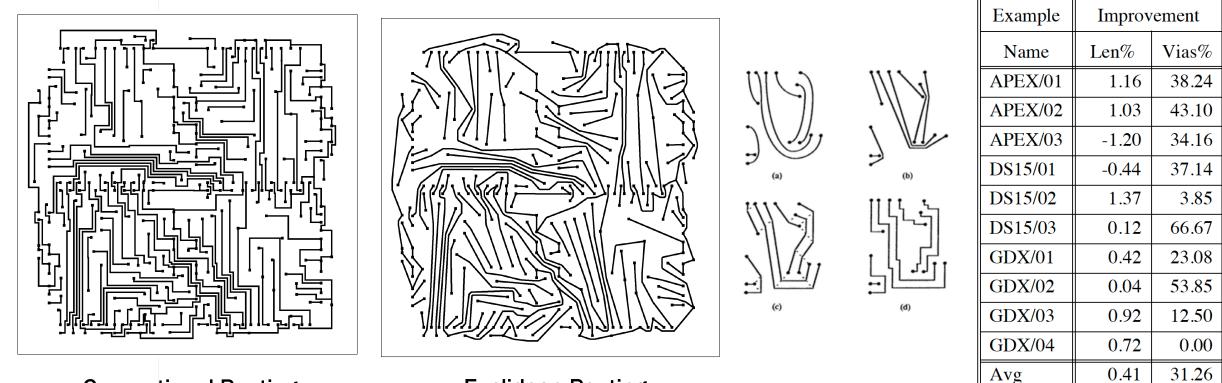

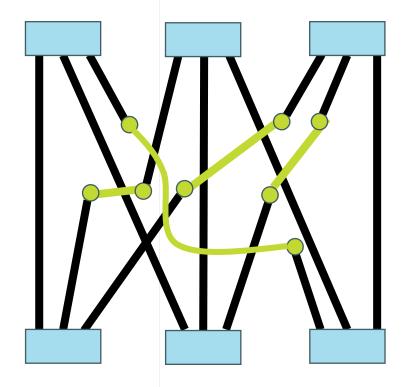

#### **Dai-Dayan Rubber Band Routing** Any angle-routing >30% avg via reduction: manufacturable now

**Conventional Routing**

**Euclidean Routing**

Source: Tal Dayan, PhD Dissertation, UC Santa Cruz, 1997

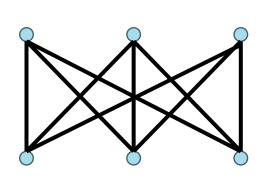

#### X Architecture Proved 30% Wire Length Reduction

#### 20% Faster Processing Time + 10% Area Reduction 斜め配線が可能な設計手法「X Architecture」による初のLSI設計について 2002年2月6日 従来手法の設計に比べ処理速度20%向上とチップ面積10%削減を実現

#

Source: ATi

EDN JUNE 28, 2006

EDN

#### WS ARCHIVE

#### Agere Leverages X Architecture in 90nm Mobile Chip

🚍 Print 👹 PDF 🖂 Email 🗬 COMMENTS O

Agere said it was impressed with the die-size reduction and reduced power dissipation resulting from the wirelength reduction achieved with the X Architecture.

Craig Garen, VP of mobility product development with Agere concluded in a statement, "Our company has confirmed that the Cadence X Architecture has realized a wirelength reduction of more than nine meters — approximately 30 percent — versus previously used Manhattan routing in the same technology. The ease with which the Cadence X Architecture integrated into our sign-off flow enabled us to meet our aggressive tape-out schedule."

### **Curvy Future: What You Design is What You Get**

### **EDA: Four Things Needed to Enable Curvy Design**

### The Debate on Curvy Design

#### **Barriers**

- Fabless needs foundry support

- Foundry needs fabless demand

- Tool infrastructure is way too inefficient for curvy design

- Perception that everything in EDA needs to change

- Benefits are unclear/unproven

• Net: It's a big change

#### **Potential Benefits**

Yield

Power

- Performance

- Area and layer-pair eliminationCost

Reduce vias and wire length

EUV and non-EUV leading edge

#### John Kibarian

#### • Founder and CEO, PDF Solutions

The Yield Management Company

- o Founded 1991

- Industry-leading data analytics and professional services towards Industry 4.0

- Public company since 2001

Current Market Cap of \$1.35B

• CMU SEMATECH Center of Rapid Yield Learning

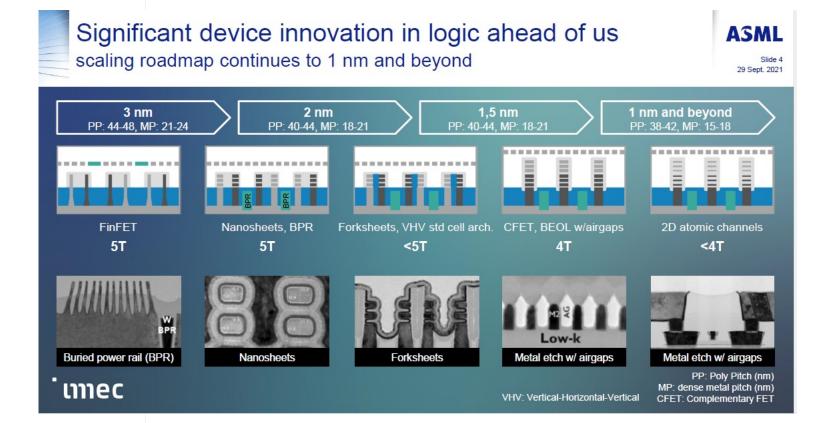

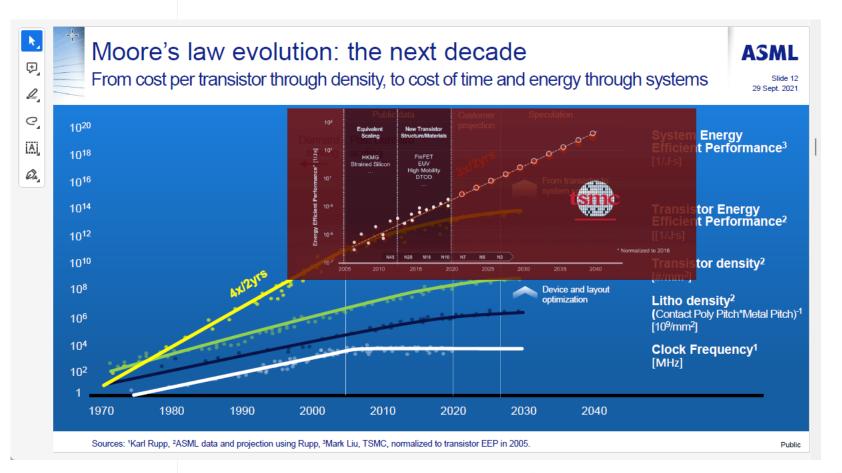

#### Moore's Law (Pitch scaling) Continues

Feature scaling is continuing but....

Metal pitch scales 30% over 4 nodes (when that used to be in 1 node)

# While Pitch Scaling Slows, Other Techniques Take Over

Device scaling, e.g., CFET

Library scaling (backside power and other techniques drop track height

Circuit innovation

System innovation

### So Why Curvy Now?

Conventional pitch scaling is projected to slow

- Library track height will continue to drop -> increasing congestion

- C-FET, backside power provide area scaling by dropping tracks

- As metal pitch scales, portion of cross section that is barrier metal increases so there is a natural tendency for resistance/sq to increase

- Reducing wire length, decreasing congestion is a needed technique so we can benefit future innovations (C-FET, library scaling, etc.)

#### **Ezequiel Russell**

Senior Director of Mask Technology, Micron Technologies

Expert in lithography, particularly for DRAM and Flash

Extensive experience with curvy masks for 193i and EUV

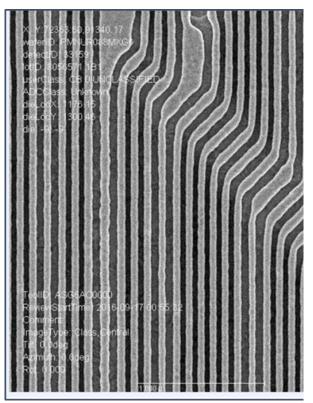

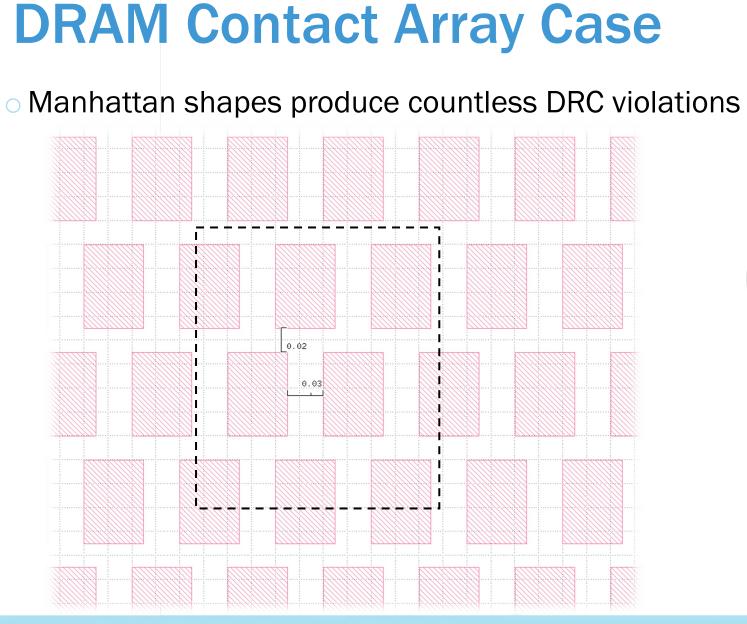

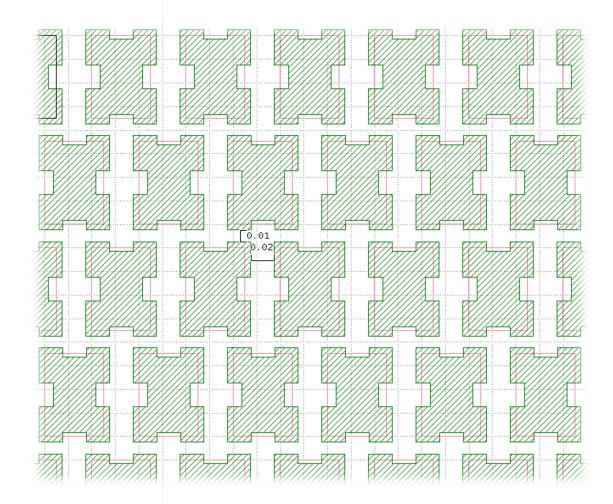

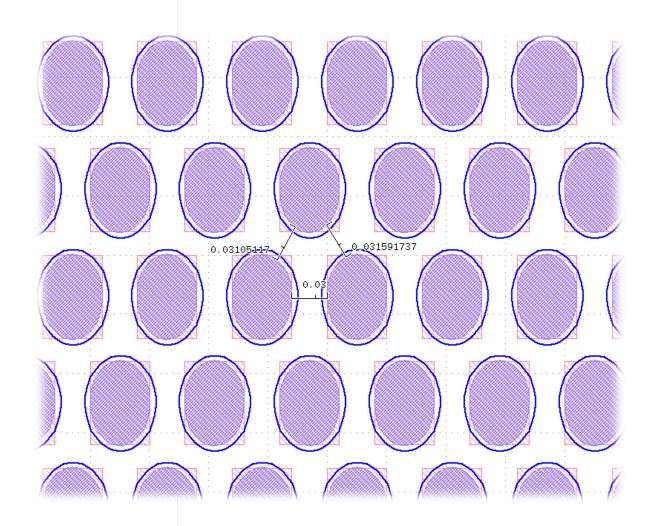

### **DRAM Contact Array Case**

- Post OPC layout

- Correcting for optical and process effects

- Constrained space for OPC solution

MRC violations

OPC mask shapes are significantly different than wafer printed pattern (Ovals)

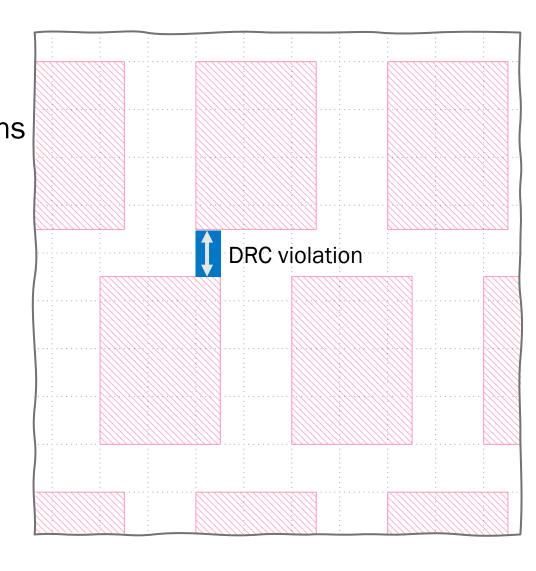

### **DRAM Contact Array Case**

#### Curvy target avoids DRC exceptions

- Curvy target facilitates OPC

No MRC constraints

- Less deviation from OPC Mask to wafer shape

Curvy shapes can be written on mask using state-of-the-art multibeam writers

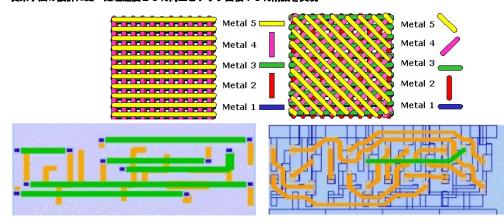

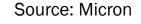

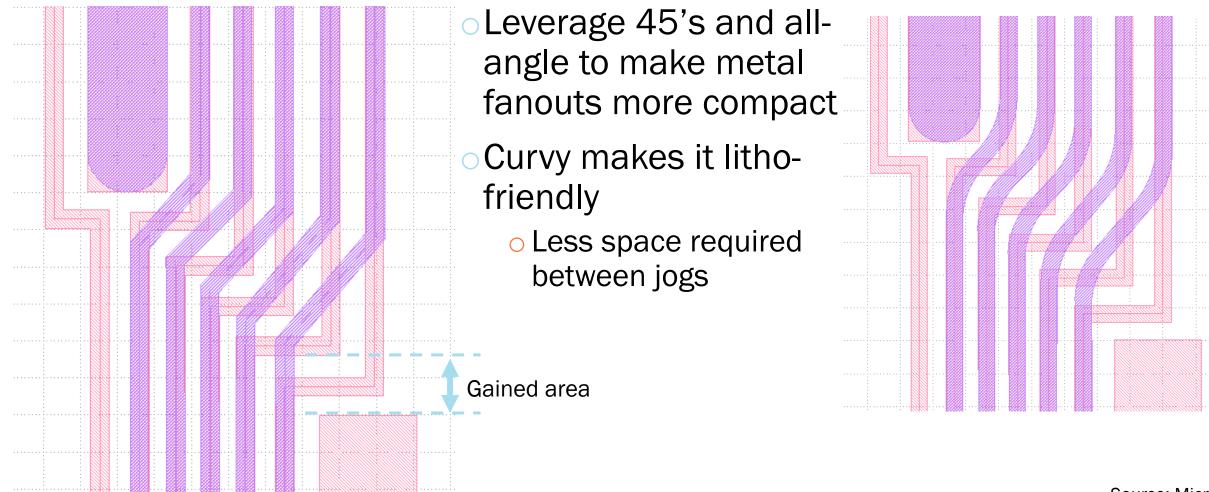

#### **Metal Routing: Non-Manhattan for Compact Layout**

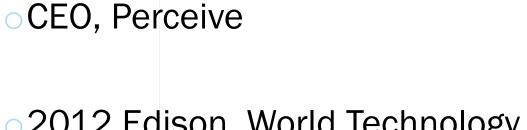

### **4-Track Jump Example**

45deg provides more compact layout and shorter routes

Manhattan jogs will need retargeting to increase width and space, taking an even larger footprint

### **Andrew Kahng**

Professor, UCSD

Director, OpenROAD Project

Blaze DFM founder, chairman and CTO

Extraction-Lithography Connection

Y Architecture

US Patent 2007/0033558 A1 Nakagawa, Kahng

and Systems, Vol. 24, No 4, April 2005

#### **Curvilinear: Perspective**

• Curvilinear is yet another potential scaling booster But ...

- $\circ$  Where and when to insert?  $\rightarrow$  alternative universes, early lockouts

- $\circ$  Chickens and eggs?  $\rightarrow$  high bar for end-to-end technology, value proofpoints

- Expect industry to make business-sensible decisions

- Past movies in same genre: "X", arguably "DFM", ...

How will the "Curvy" movie be different?

- Quest for (cost, value) scaling is more desperate today

- OTOH, today's audience is much smaller, more consolidated, more risk-averse, ...

• No question: A new (and mind-blowing!) paradigm for physical structure

### **Curvilinear: Thoughts**

#### OWhich IC product organizations are most excited by curvilinear?

#### • What are the top-K limiters?

- IP ecosystem

- Device-layer patterning

- Alignment, resolution, anisotropy ...

- Row-based standard-cell architecture

- + finite oxygen supply: backside power, 2.5D/3DHI, ... + other uses for 340,000,000x compute!

- + hazy insertion point: node, layer, die ASP, product PPAC, ...

- + stopping points of virtuous cycles: recapturable die area, density downsides, ...

#### • What blocks collaborative enablement?

- IP moats and unknown cost uplifts

- Incentives to bring up ecosystem elements ("pioneers get the arrows")

o Can we discuss blockers and unblockers today?

2012 Edison, World Technology Awards

Tangent Over-the-Cell

• X Architecture

**Steve Teig**

BioCAD, Combichem

• Tabula, Perceive

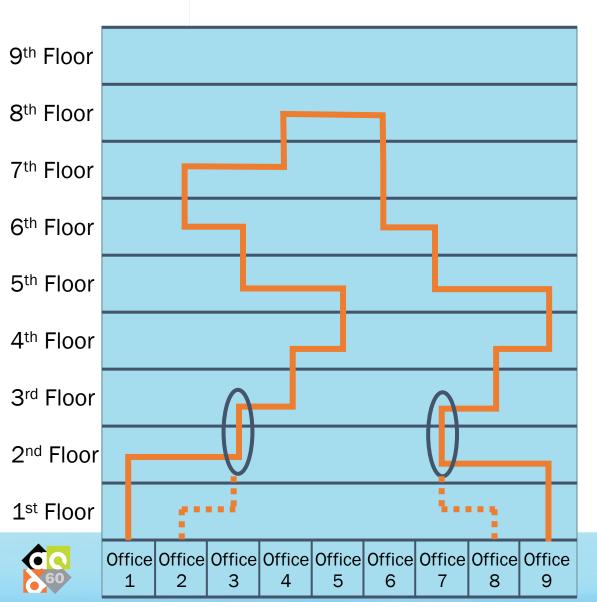

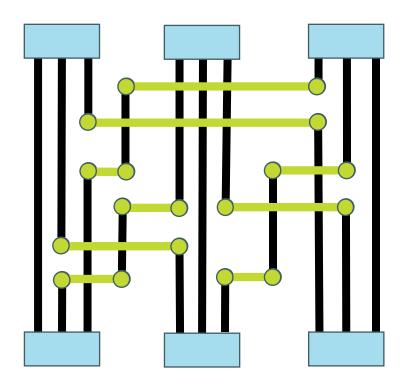

### **Vias Are the Enemy**

#### Create congestion: pebbles in the stream

- Vias in lower layers are particularly bad

- Manhattan routing almost always needs 2+ vias in lower layers

- $_{\odot}$  Every turn needs at least 2 vias

- Added vias come in pairs

- Curvy routing rarely needs any vias for short connections in lower layers

- Vias are physically unreliable

- $_{\odot}$  Delay has high uncertainty ightarrow conservatism

- Reducing vias can reduce wire length a lot!

Reducing vias can reduce cost

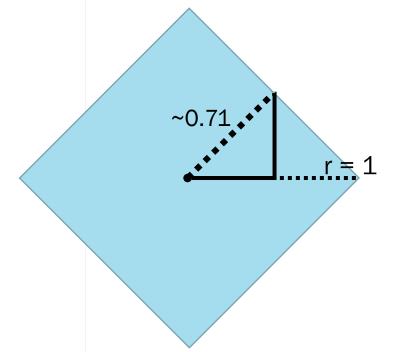

#### Virtuous Cycle: Less Wire = Less Area = Less Wire...

Manhattan placement, curvy (Euclidean) routing:

$$\int_0^1 \sqrt{y^2 + (1-y)^2} \, dy = \frac{2 + \sqrt{2} \ln(1 + \sqrt{2})}{4} = \sim 0.81$$

hattan placement, curvy (Euclidean) routing:

$$\sqrt{y^2 + (1-y)^2} \, dy = \frac{2 + \sqrt{2} \ln(1 + \sqrt{2})}{4} = \sim 0.81$$

$$A = \sim 0.636$$

$$36.3\% \text{ area shrink!}$$

$$L = 0.81 * \sqrt{0.81} * \sqrt{0.81} = 0.69$$

$$L = 0.81 * \sqrt{0.81} = 0.73$$

$$A = 1$$

$$L = 1$$

Wirelength is x% smaller  $\Rightarrow$  routing area is x% smaller  $\Rightarrow$  chip area is x% smaller  $=$

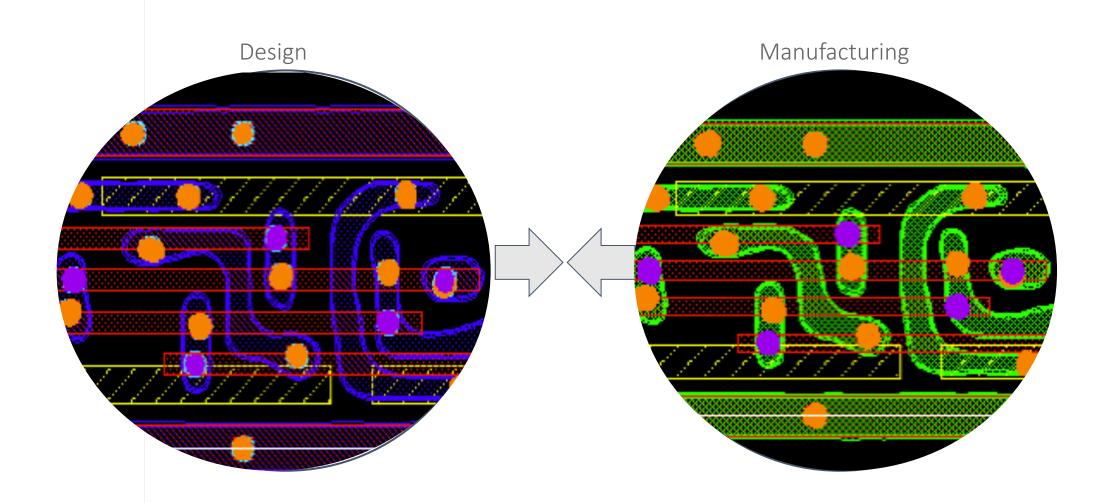

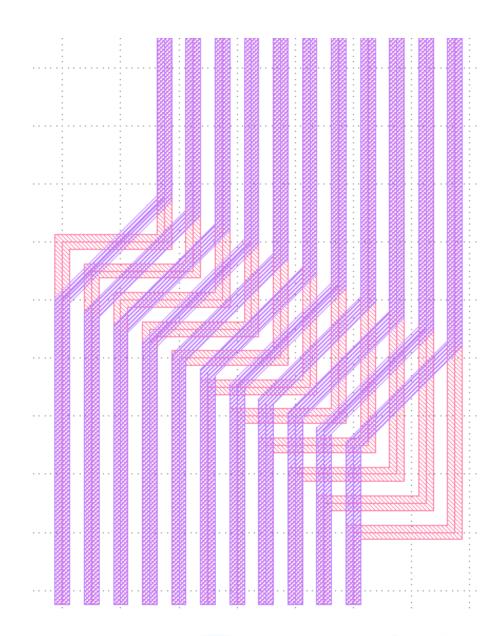

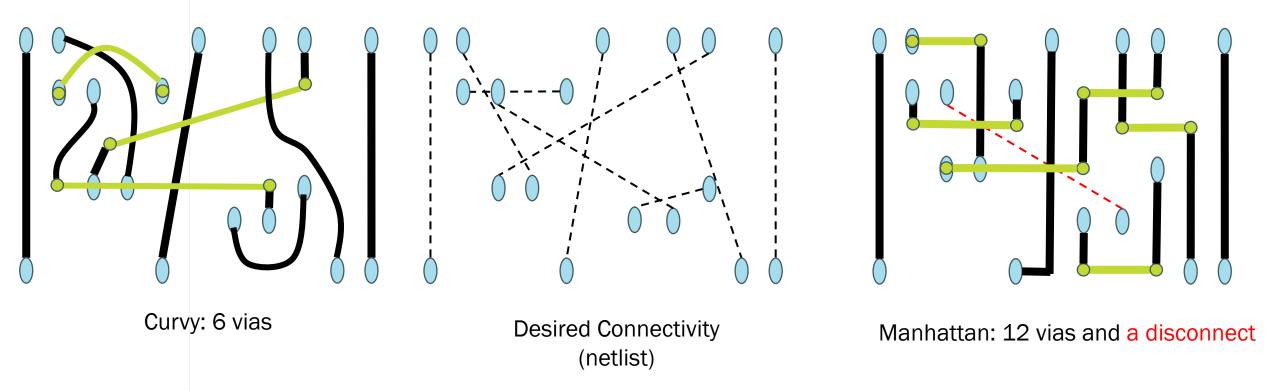

### **Curvy Can Reduce Via Counts by >50%!**

Curvy: 4 via pairs

Manhattan: 9 via pairs

### **Curvy Can Reduce Via Counts by ~50%!**

#### **Curvy is a Transformative P&R Technology**

Should reduce wiring area by 33-40% vs. Manhattan

Using curvy placement and curvy routing: "virtuous cycle"

Should reduce via counts by ~50% vs. Manhattan

Should reduce via counts by ~50% vs. Manhattan

- Massively reduces detouring and wiring congestion

- First-order effect that is not contemplated by simplistic wire length models

Remove 2 layers of interconnect – maybe even 3 for 9+ signal layers

Or reduce die size by 10-15% and remove 1 layer of interconnect

And reduce performance conservatism (due to manufacturing variability)

Which will improve yield, too

# Why is Curvy Design an Opportunity Now?

Moderator:

Panel:

Aki Fujimura, CEO, D2S, Inc.

John Kibarian, CEO, PDF Solutions Ezequiel Russell, Sr. Director of Mask Technology, Micron Andrew Kahng, Professor, UCSD Steve Teig, CEO, Perceive 01010 10401 41m

â

### The Debate on Curvy Design

#### **Barriers**

- Fabless needs foundry support

- Foundry needs fabless demand

- Tool infrastructure is way too inefficient for curvy design

- Perception that everything in EDA needs to change

- Benefits are unclear/unproven

• Net: It's a big change

#### **Potential Benefits**

Yield

Power

- Performance

- Area and layer-pair eliminationCost

Reduce vias and wire length

EUV and non-EUV leading edge