Aki Fujimura, CEO D2S, Inc. | August 22, 2025 for the SPIE BACUS Webinar Series

### Ask for What You Can Get and Get What You Ask For

All manufacturable shapes are curvy

D2S Patented Technology. • Copyright 2018-2025, D2S, Inc. D2S® and TrueMask® are US-registered trademarks of D2S, Inc. in US. TrueMask® and TrueModel® are registered trademarks of D2S, Inc. in US, Japan, Korea, China and Taiwan.

### **Ezequiel was Right...**

### **Why Curvilinear Masks**

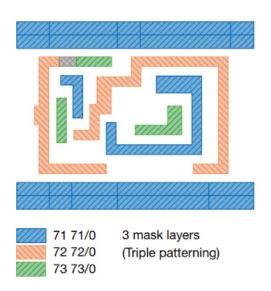

### More degrees of freedom for OPC solutions Assist features: improved process window, optimal

- placement

- Main features: infinitesimally small segmentation of OPC, higher degree of control of the correction

- Physically meaningful MRCs (no corner-to-corner)

- Accurate target representation for Mask <u>and</u> Wafer

Mask Fidelity

- Improved matching between mask and intended OPC shapes

- -More accurate OPC models

- No need to compensate for differences between "intended" shape and mask shape

- Mask friendly shapes (no sharp corners)

- Mask uniformity: reduces variations at feature corners

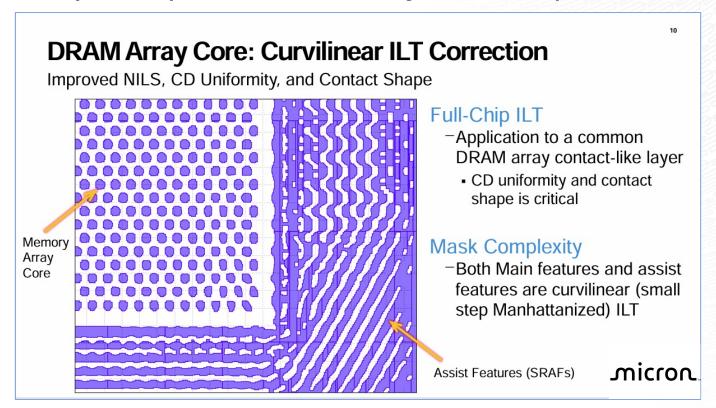

micron

### Space of all Shapes is Very Large

### Space of All Manufacturable Curvilinear Shapes is Very Small

<del>-</del>5

### No Manhattan Shape is Manufacturable

1D CD of Manhattan Shapes ARE Manufacturable

### Wafer Designs are Made So Only 1D CD is Important

Design is resilient to misalignment and corner rounding

This is bad, but it's a compromise

### 2D Matters on Mask, a lot

"Easiest way to improve CDU on wafer is to improve it on mask"

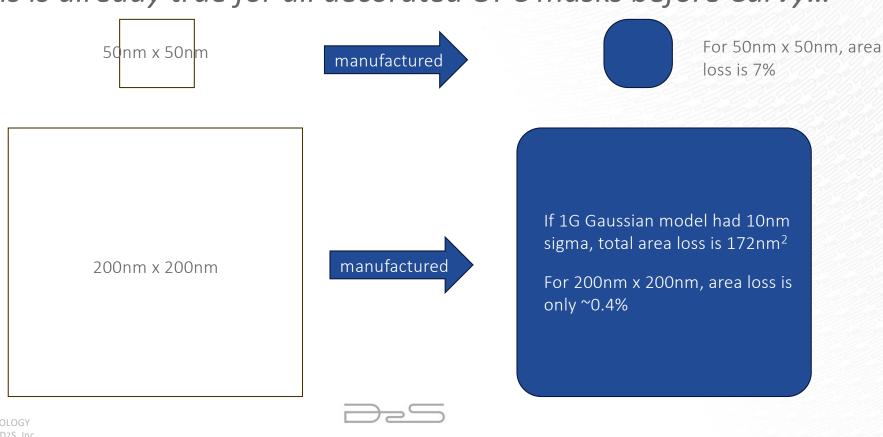

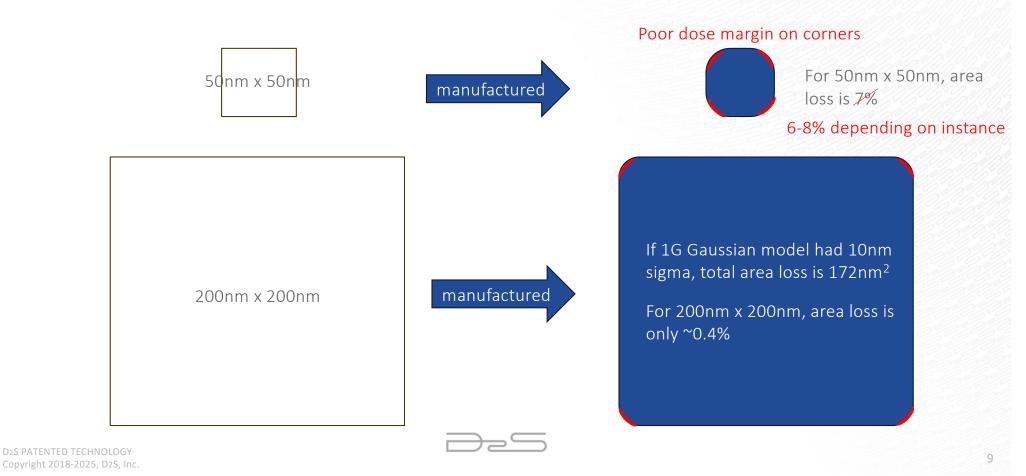

### Wafer Accuracy is About Area Accuracy on Mask

So smaller shapes we need to handle now can't be doing 1D This is already true for all decorated OPC masks before Curvy...

D<sub>2</sub>S PATENTED TECHNOLOGY Copyright 2018-2025, D<sub>2</sub>S, Inc.

### **Dose Margin is Important**

Instance-to-instance variation is critical for manufacturing

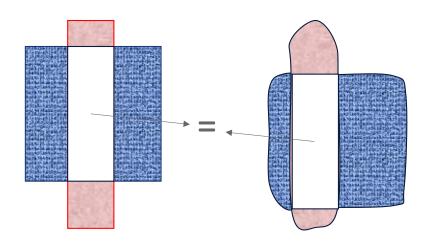

### Much Better to Ask for What You can Get

Instance-to-instance variation is critical for manufacturing

No area loss in nominal And less variation

Trying to manufacture this and getting this has more variation than trying to manufacture this

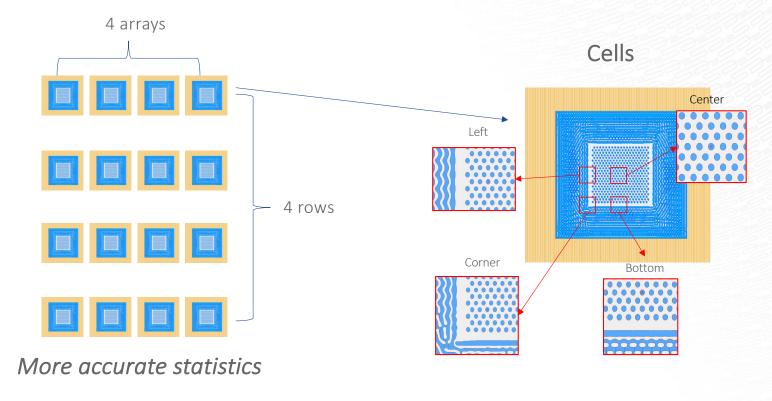

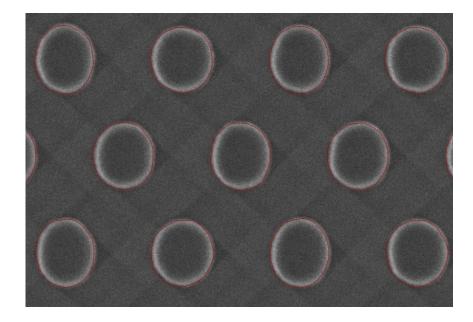

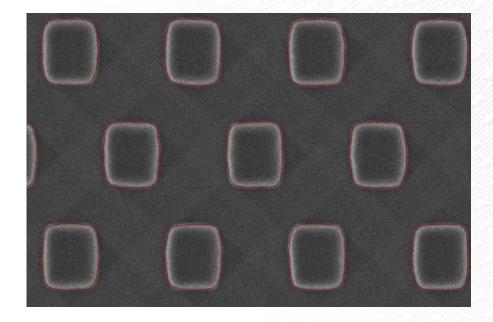

## Study of Mask Variation with 16 Copies of Curvilinear Mask and Manhattan Mask Written by Multi Beam

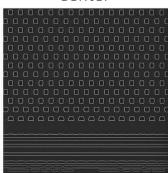

### SEM Images are Collected for 4 Locations of Contact Array

Center

Bottom

Cu

Left (mirrored)

Corner

Curvilinear

Center

Bottom

Manhattan

Left (mirrored)

Corner

D2S PATENTED TECHNOLOGY Copyright 2018-2025, D2S, Inc.

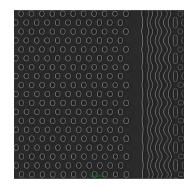

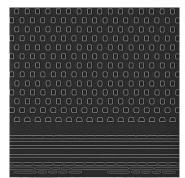

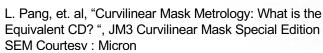

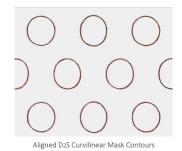

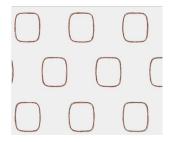

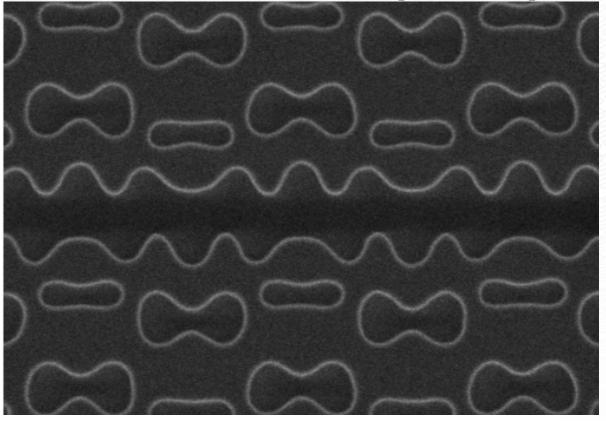

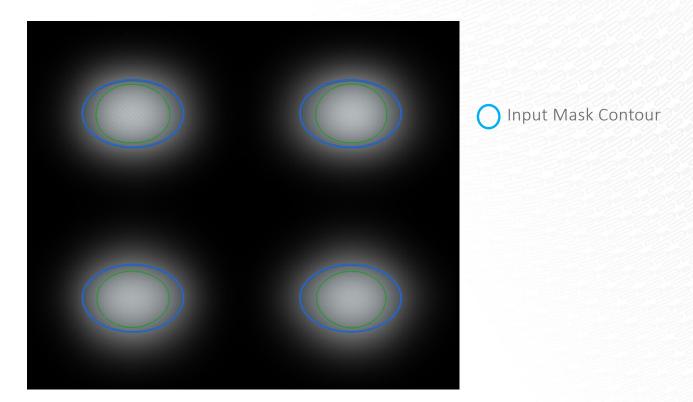

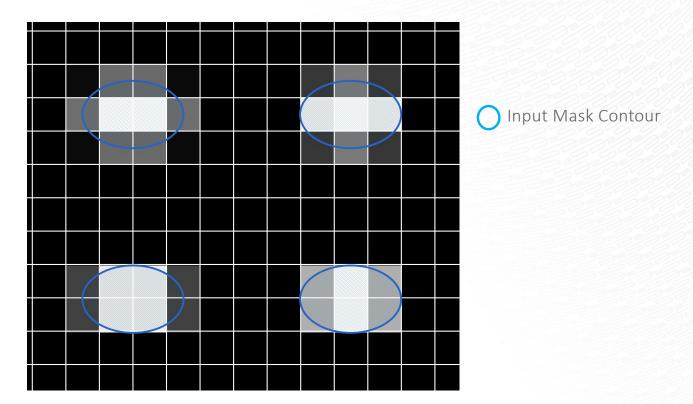

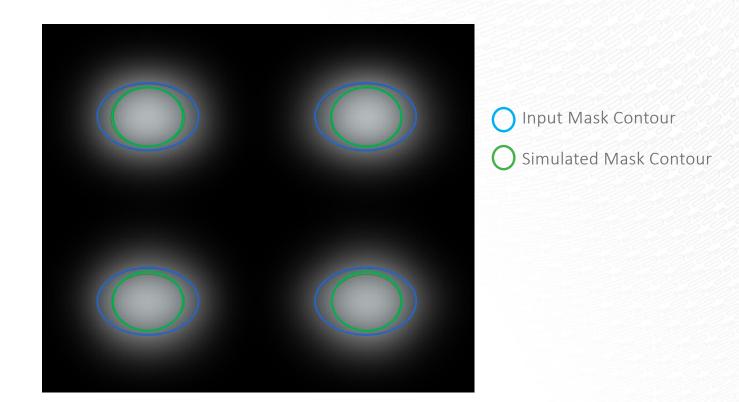

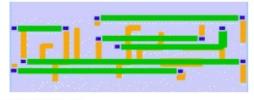

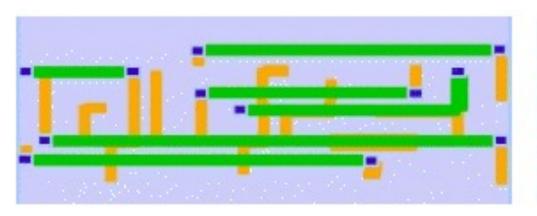

## For Each Location 16 SEM Images are Aligned and Contours are Extracted to Form Variation Band

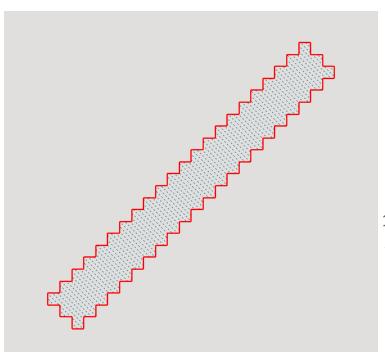

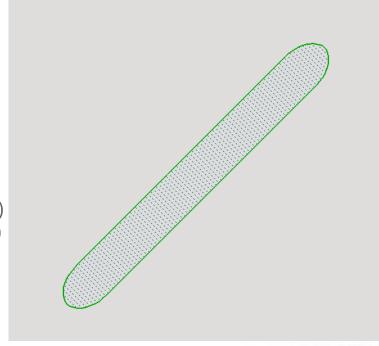

### **Center: Mask Contours Extracted**

Curvilinear Mask Pattern

Manhattan Mask Pattern

L. Pang, et. al, "Curvilinear Mask Metrology: What is the Equivalent CD? ", JM3 Curvilinear Mask Special Edition SEM Courtesy: Micron

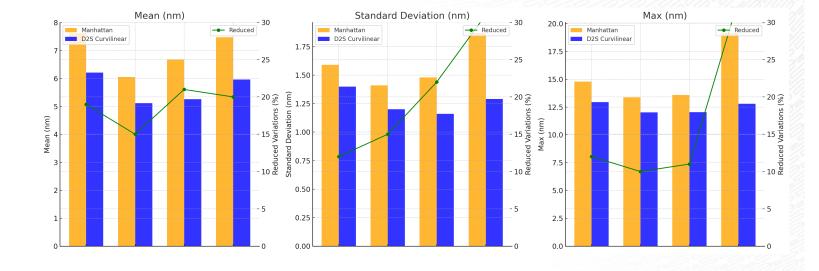

### Curvilinear Reduced Mask Variation by ~20%

This will translate to wafer variation on every chip

L. Pang, et. al, "Curvilinear Mask Metrology: What is the Equivalent CD?", JM3 Curvilinear Mask Special Edition

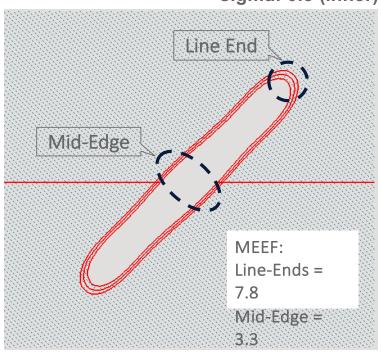

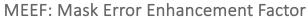

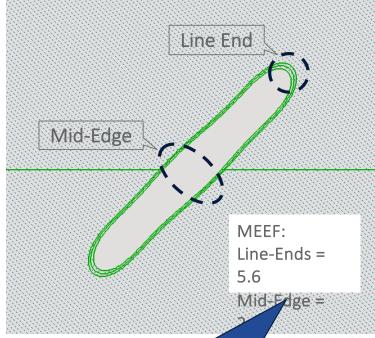

### Let's Look at MEEF: Mask Effect on Wafer

MEEF: Mask Error Enhancement Factor

Design Width 144 nm (Mask) 36 nm (Wafer)

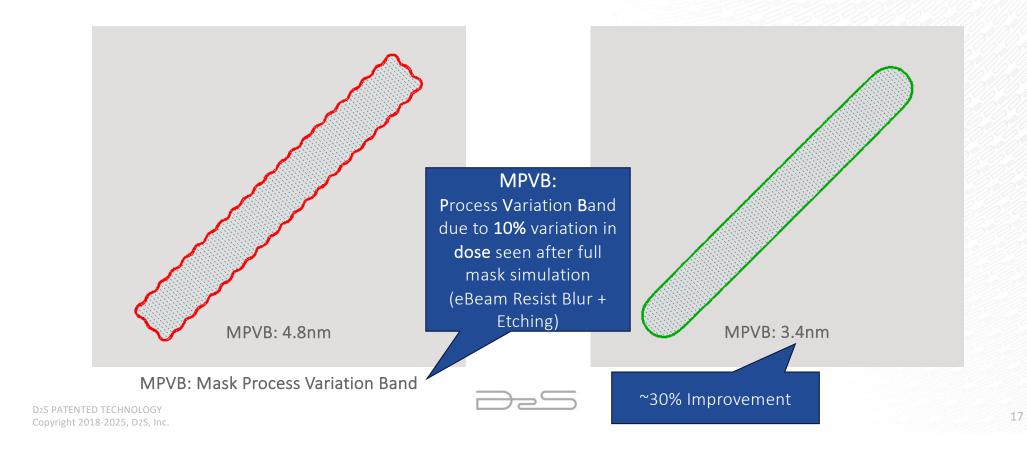

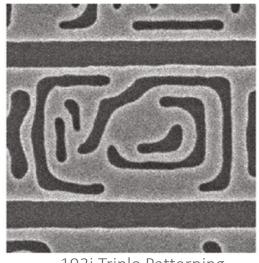

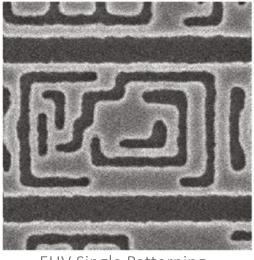

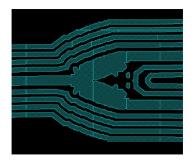

### Smooth Diagonals Are More Manufacturable On Mask

### **And Smooth Diagonals Provide Better MEEF**

193i with 1.35 NA and a composite light source sigma: 0.5 (inner) 0.9 (outer) and TE polarization

~28% Improvement

### Manufacturable Shapes are More Reliably Manufactured

# Ask for What You Can Get And Get What You Asked For

This should guide what we mean by "curvilinear"

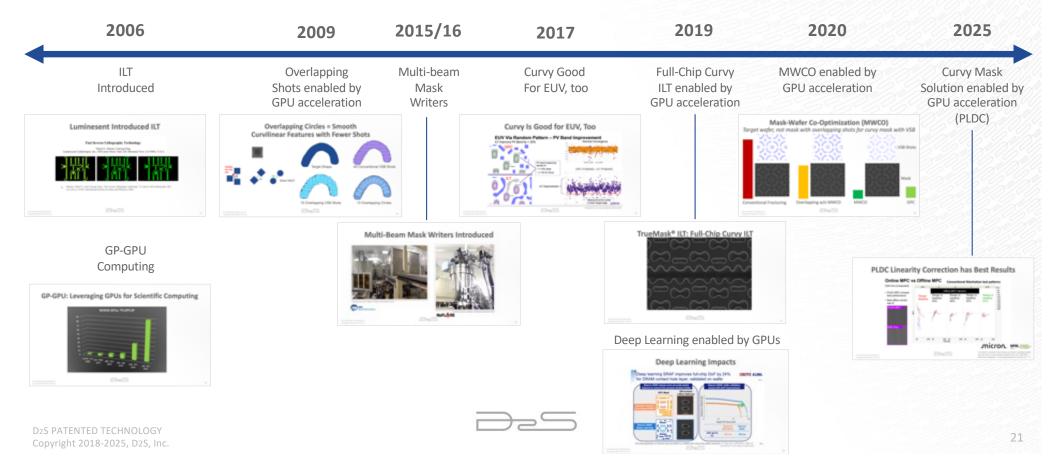

### **Curvy Masks and GP-GPUs Both Started in 2006**

Got Enabled by Multi-Beam Mask Writing

### **Luminesent Introduced ILT**

#### Fast Inverse Lithography Technology

Daniel S. Abrams, Linyong Pang Luminescent Technologies, Inc., 650 Castro Street, Suite 220, Mountain View, CA 94041, U.S.A.

1. Abrams, Daniel S., and Linyong Pang. "Fast inverse lithography technology." In *Optical Microlithography XIX*, vol. 6154, p. 61541J. International Society for Optics and Photonics, 2006.

### **GP-GPU: Leveraging GPUs for Scientific Computing**

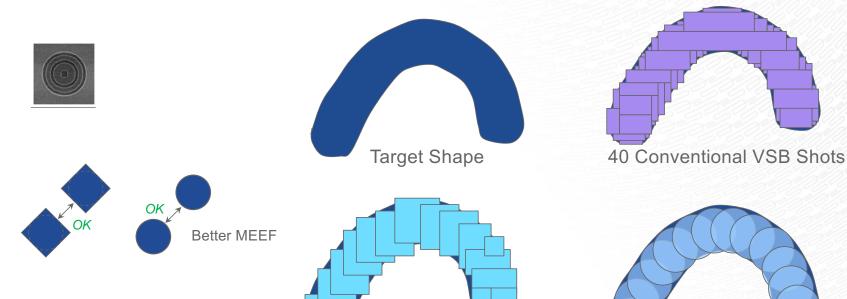

### Overlapping Circles = Smooth Curvilinear Features with Fewer Shots

15 Overlapping VSB Shots

Violates min dist rule

13 Overlapping Circles

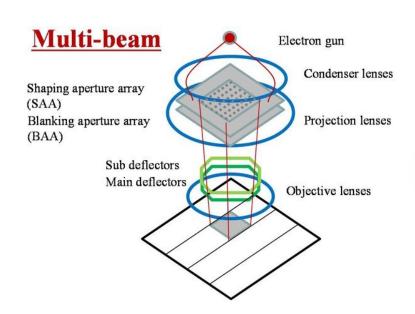

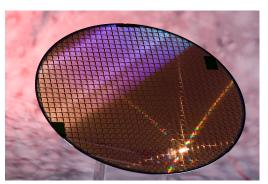

### Multi-Beam Mask Writers Introduced

Prototype pictured. eBeam Initiative presentation 2015

### Curvy Is Good for EUV, Too

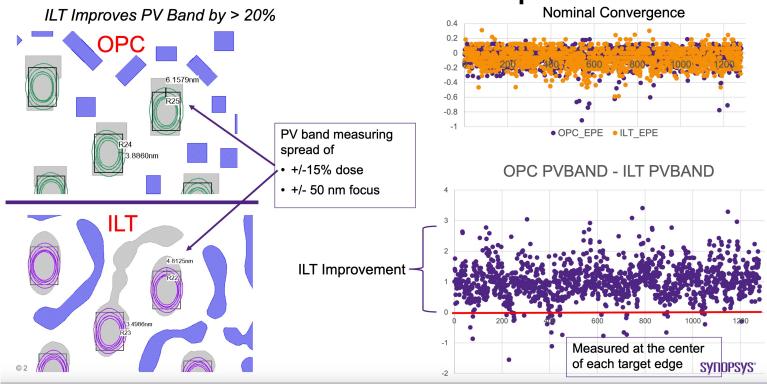

### **EUV Via Random Pattern – PV Band Improvement**

Presented by Tom Cecil at eBeam Initiative 2017

TrueMask® ILT: Full-Chip Curvy ILT

### **Deep Learning Impacts**

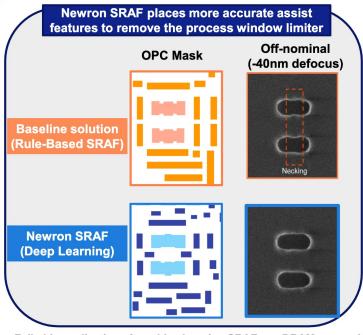

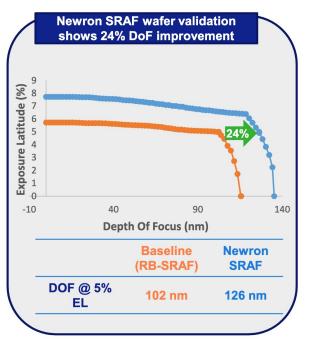

Deep learning SRAF improves full-chip DoF by 24% for DRAM contact hole layer, validated on wafer

Slide 1

Public

Full-chip application of machine learning SRAFs on DRAM case using auto pattern selection K. Chen et al., SPIE 2019, 10961-37

Presented by Yu Cao, eBeam Initiative 2019

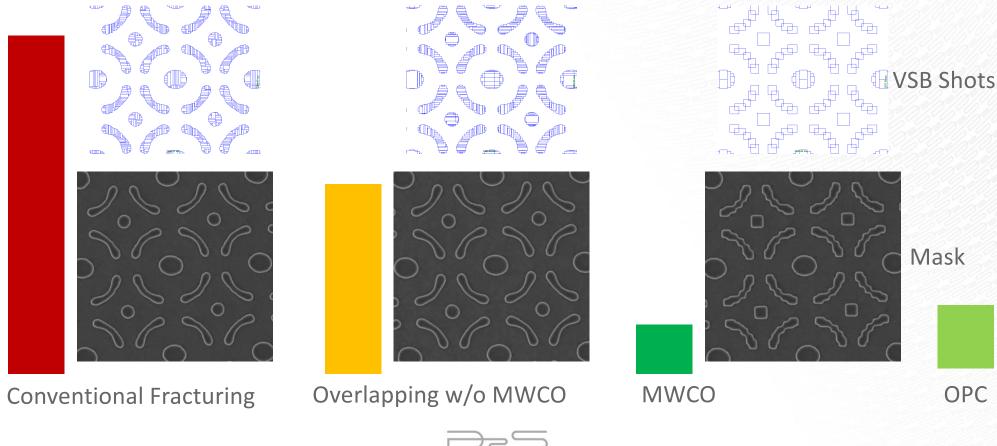

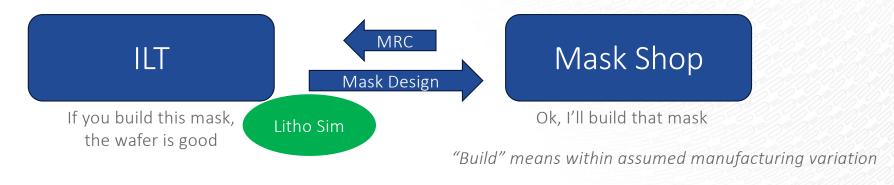

### Mask-Wafer Co-Optimization (MWCO)

Target wafer, not mask with overlapping shots for curvy mask with VSB

D<sub>2</sub>S PATENTED TECHNOLOGY Copyright 2018-2025, D<sub>2</sub>S, Inc.

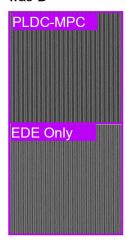

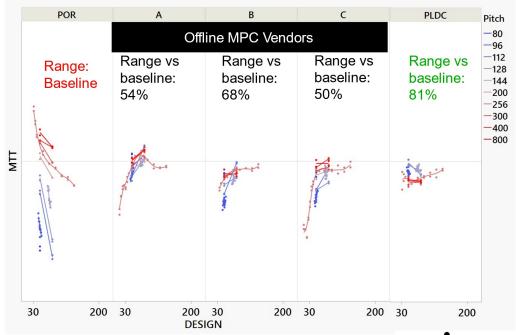

### **PLDC Linearity Correction has Best Results**

### Online MPC vs Offline MPC

**Conventional Manhattan test patterns**

Dark line (unexposed)

- PLDC-MPC showed best performance

- Best offline vendor was B

Full-reticle Curvilinear inline linearity correction including variable bias with zero turnaround time, Spinelli, Paris, et al, 2025 SPIE Advanced Lithography + Patterning Symposium, San Jose, CA 30

### So Curvilinear Masks Can be Manufactured

And it's better for wafer process window

Any other barriers to adoption?

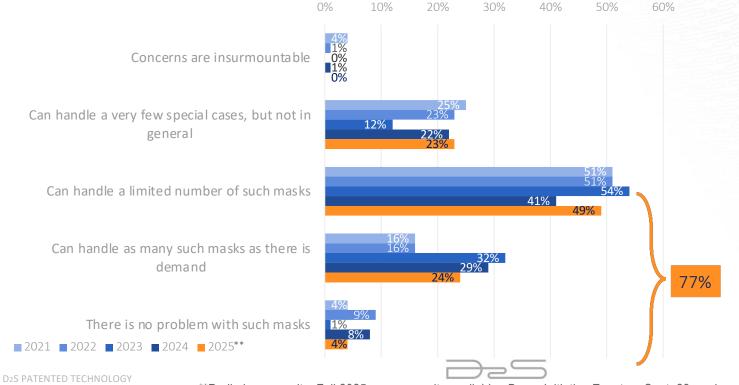

### Confidence Remains High for Curvilinear But reality may be setting in on some barriers

eBeam Initiative Luminaries Surveys 2021-2025\*\*:

Are the problems with HVM of masks containing curvilinear features

insurmountable for leading-edge mask shops by the end of next year? Select the statement that you agree with most. 10% 40%

At least a limited number of masks being curvy is okay for leading-edge mask shops:

Copyright 2018-2025, D2S, Inc.

\*\*Preliminary results. Full 2025 survey results available eBeam Initiative Event on Sept. 23 or ebeam.org

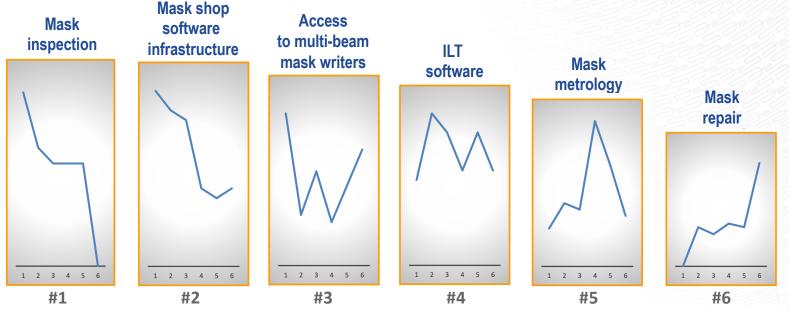

# Views of Challenges Change: 2021-2025\*\*

eBeam Initiative Luminaries Surveys 2021-2025: Please rank your biggest concerns in producing curvilinear masks

Note: 1-6 on X-axis indicate # of respondents that ranked that question as that ordinal number with 1 = highest

<sup>\*\*</sup>Preliminary results. Full 2025 survey results available eBeam Initiative Event on Sept. 23 or ebeam.org

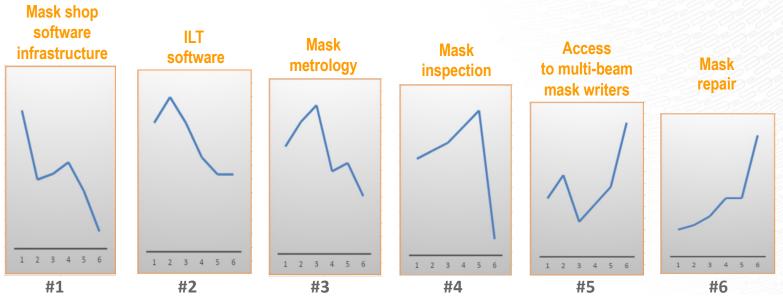

# Views of Challenges Change: 2021-2025\*\*

**eBeam Initiative Luminaries Surveys 2025:** Please rank your biggest concerns in producing curvilinear masks

Note: 1-6 on X-axis indicate # of respondents that ranked that question as that ordinal number with 1 = highest

<sup>\*\*</sup>Preliminary results. Full 2025 survey results available eBeam Initiative Event on Sept. 23 or ebeam.org

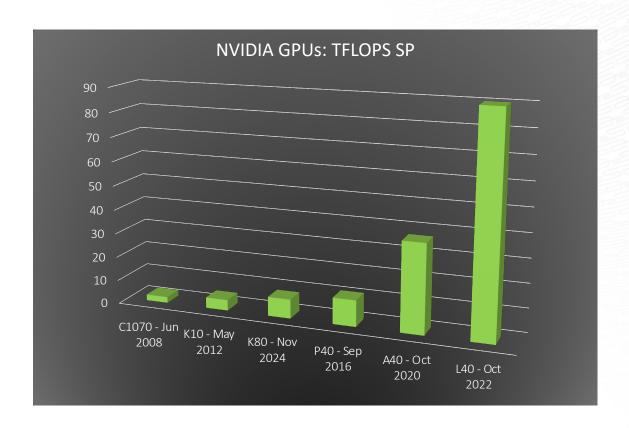

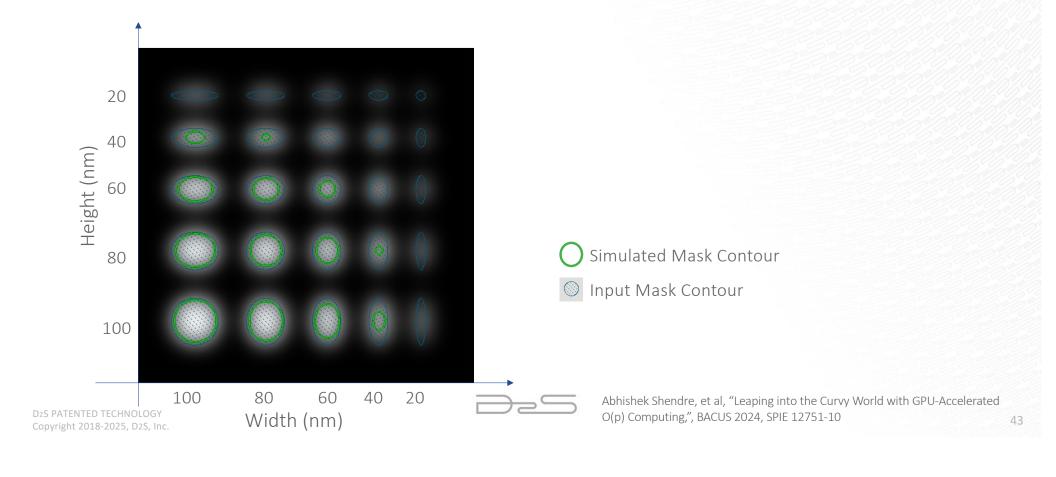

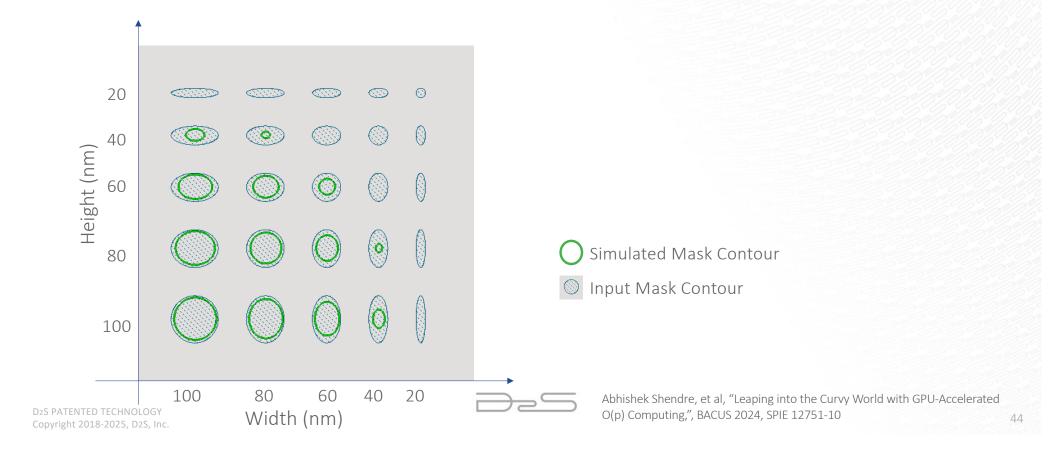

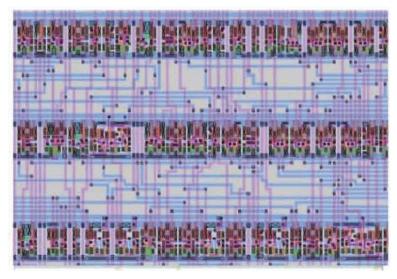

## Pixel Based Computing With GPU Acceleration Is Natural For Multi-beam Writers

O(p) Runtime Is Bounded By Number of Pixels

Abhishek Shendre, et al, "Leaping into the Curvy World with GPU-Accelerated O(p) Computing,", BACUS 2024, SPIE 12751-10

### Rasterization is a Digital Sampling of Vector Shapes

- Rasterization is 2D sampling of spatial information

- Shannon-Nyquist sampling of 1D audio data from WW II in 2D

- Magic of rasterization creates smooth curves by low-pass filtering of the processes

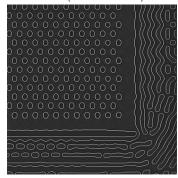

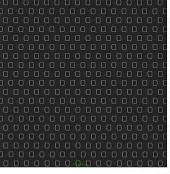

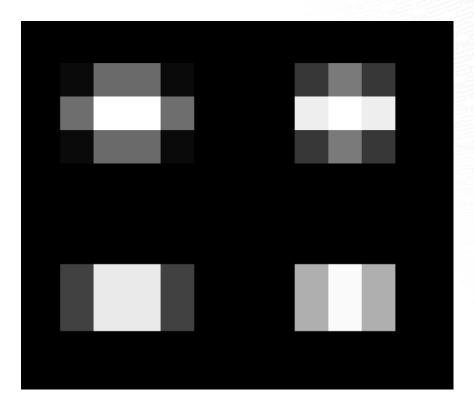

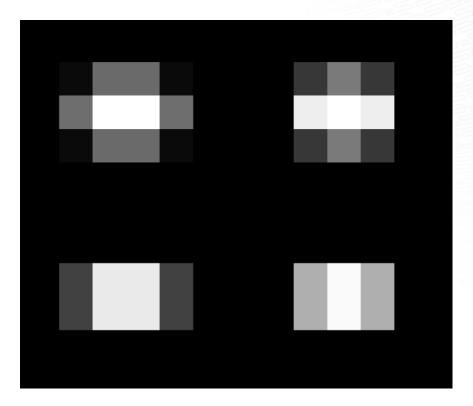

# **Guess What Shapes These Pixels Represent?**

# Different Pixel Alignment of the Same Shapes

Abhishek Shendre, et al, "Leaping into the Curvy World with GPU-Accelerated O(p) Computing,", BACUS 2024, SPIE 12751-10

## Different Pixel Alignment of the Same Shapes

Abhishek Shendre, et al, "Leaping into the Curvy World with GPU-Accelerated O(p) Computing,", BACUS 2024, SPIE 12751-10

# **Totally Different Pixel Maps Are For the Same Shape**

Abhishek Shendre, et al, "Leaping into the Curvy World with GPU-Accelerated O(p) Computing,", BACUS 2024, SPIE 12751-10

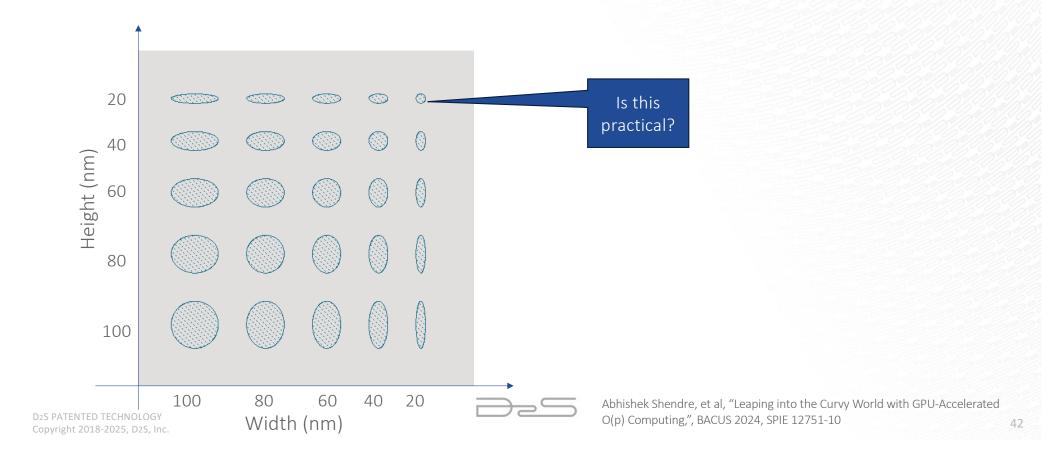

# **Small Shapes and Sharper Angles Need Help**

# How Small/Sharp Can We Go?

## **Very Small Shapes May Not Resolve**

# We Need Mask Rules to Check Manufacturability

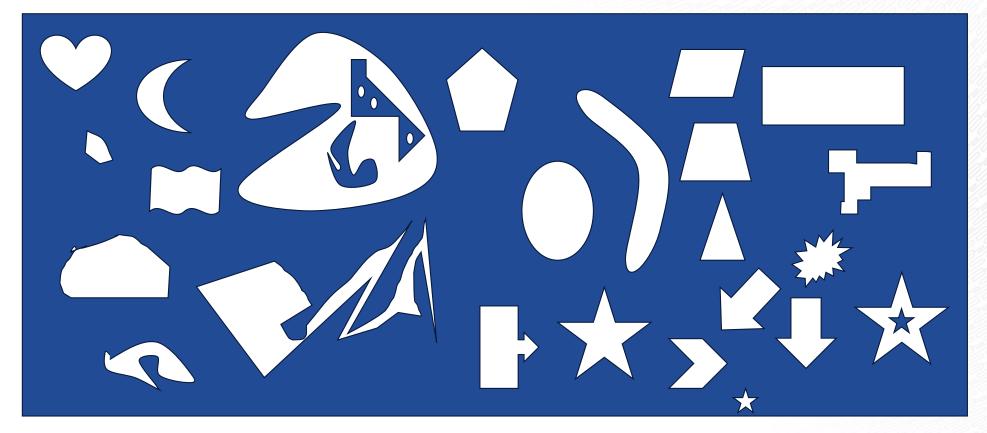

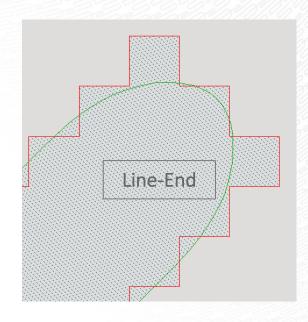

#### **Curvilinear Mask Rules Need to Be a Little Different**

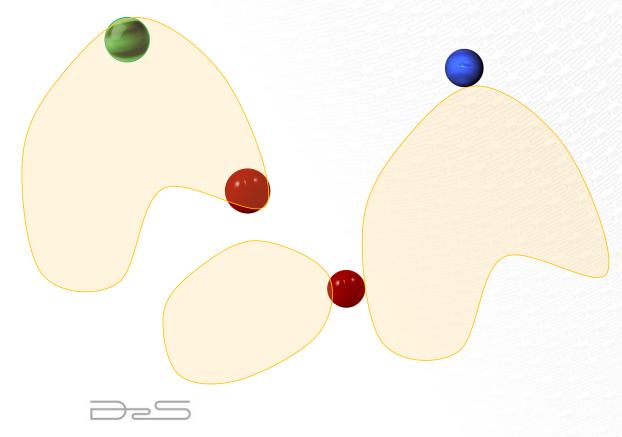

Rolling Balls for minimum Curvature, CD, Space, and Area

D<sub>2</sub>S PATENTED TECHNOLOGY Copyright 2018-2025, D<sub>2</sub>S, Inc.

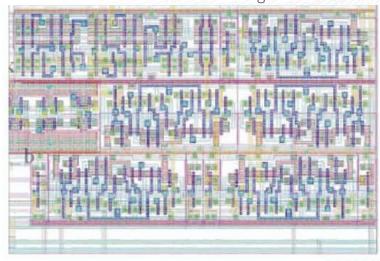

#### Multibeam Mask Writers Enabled Curvy Masks

Curvy Masks Enabled Curvy ILT

GPU-Acceleration with O(p) Solves Software Infrastructure

Full-chip curvy designs are now manufacturable

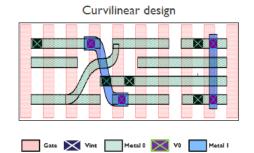

## **Curvy ILT enables Curvy Design**

Multibeam Mask Writers Enabled Curvy Masks

Curvy Masks Enabled Curvy ILT

GPU-Acceleration with O(p) Solves Software Infrastructure

Full-chip curvy designs are now manufacturable

#### Wafer Simulated to the Manufactured Mask

Exactly, if ILT outputs Manufacturable Mask Shapes

- Wafer quality on the average is better

- Because mask shape is exactly what ILT simulated

- Wafer variation is reduced because mask variation is reduced

- And because curvilinear ILT has much better process windows

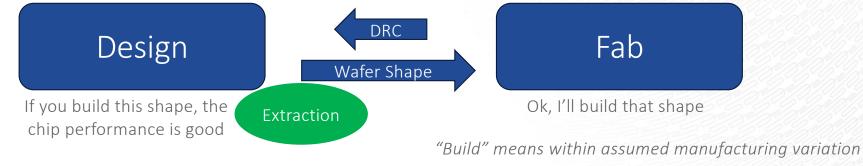

#### **Exactly the Same Will be True with Curvy Design**

Substantially reduce timing margin by getting what you assumed

- Manufacturing should restrict curvy design to manufacturable curvy

- Designers assume some uniform deformation of Manhattan design today

- Parasitic extraction uses some rule-based guess of uniform deformations

- But reality is per-instance and environment-specific deformation

## Don't Ask for the Impossible and then Guess How Far Off

Ask for what can be manufactured and get it

**EUV Single Patterning**

#### From imec

Source: "Next-generation lithography – an outlook on EUV projection and nanoimprint", Jan van Schoot and Helmut Schift, June 8, 2017, de Gruyter, Advanced Optical Technologies, 2017, 6(3-4): 159-162, DOI 10.1515/aot-2017-0040

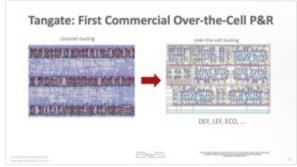

#### 21 years in Physical Design EDA; 21 years in Manufacturing

I'm a hybrid...

1979 1982 1984 1986 1987 1991 1993 1997 1999 2001 2002 2006 2009 2019 2025 Al Student DA MTS Founder/ Product Mgr VP. CE @Pure Fire & Ice Χ MAD & D<sub>2</sub>S TrueMask® TrueMask® Curvy Mask VP Eng. @Simplex BS, MS @MIT @Trilogy DF II QX Architecture DAM founded MDP ILT Solution MTS Tancell: Tangate: Co-op in DA @Tangent First First Rep for CFI First fast announced DFM & CTO (spin out First GPU- Industry's (PLDC) from @Cadence P&R A\* router commercial commercial from Accelerated First Full- D2S Awarded Cadence @Honeywell system to over-the-cell (acquisition) extraction Cadence) MDP Chip Curvy Best Poster to have timing P&R (acquisition) ILT/OPC Tekscend and @SPIE AL Best Paper to assurance and system LEF/DEF **ATG** Micron ECO @PhotoMask Japan

# Tangate: First Commercial Over-the-Cell P&R

channel routing

over-the-cell routing

DEF, LEF, ECO, ...

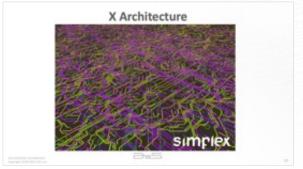

## **X** Architecture

### 30% Wire Length Reduction from X By Many Customers

Curvy design is a superset of X Architecture

#### 20% Faster Processing Time + 10% Area Reduction 斜め配線が可能な設計手法「X Architecture」による初のLSI設計について

Metal 4 Metal 3 Metal 2

......

#### X Facts from 16 production chips

- -30% wirelength -10% area

- -40% vias

- Reduce 1 layer pair

- +20% performance Faster design cycles

Copyright 2018-2025, D2S, Inc.

#### **Toshiba Used X Inside Standard Cells**

Using X Architecture both for intra- and inter-connect

斜め配線が可能な設計手法「X Architecture」による初のLSI設計について

2002年2月6日

従来手法の設計に比べ処理速度20%向上とチップ面積10%削減を実現

#### **TOSHIBA**

#### 2025-2035

Litho Scaling is Almost Over: Devices are Going 3D

Power (and clock?) is Going to Backside

Even more interconnect limited than now

Interconnect in M2 and up can go any direction

**Curvy routing is the answer**

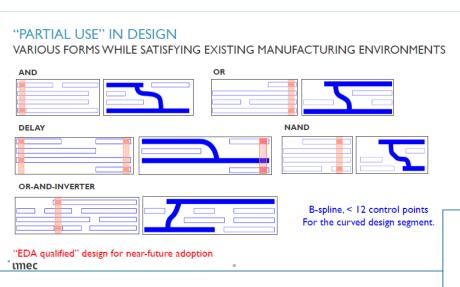

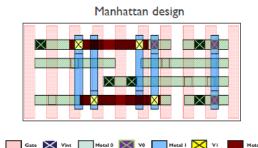

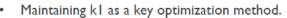

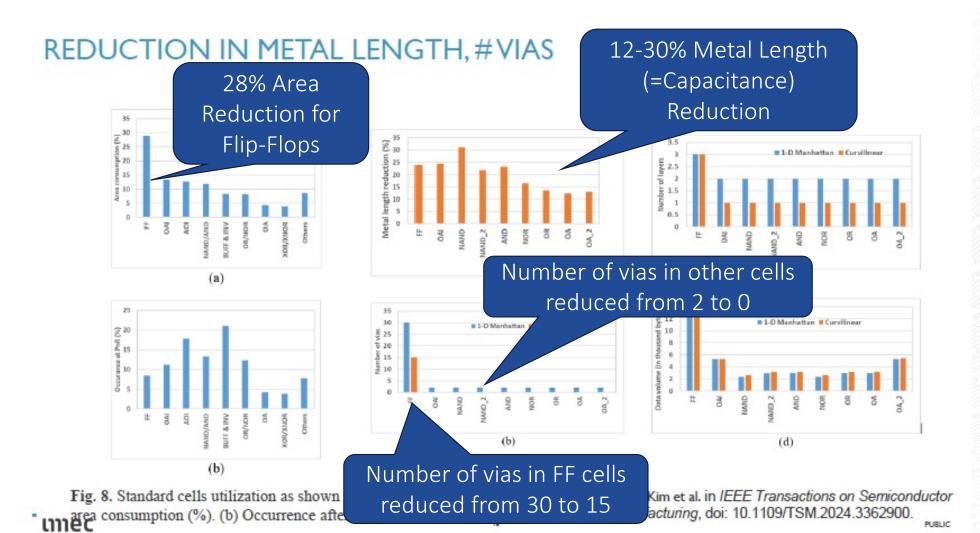

#### IMEC Has Been Publishing on Curvy Design

MANUFACTURING-FRIENDLY CURVILINEAR STANDARD CELL DESIGN

RYOUNG-HAN KIM, APOORVA OAK, YASSER SHERAZI, GIOELE MIRABELLI, SOOBIN HWANG, KIHO YANG, HSINLAN CHANG

PUBLIC

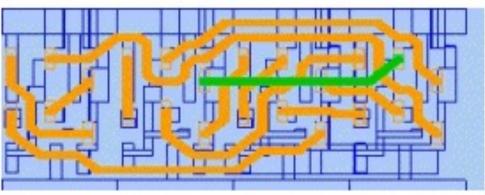

#### ULTIMATELY – "FREE-FORM USE" IN LOGIC DESIGN ULTIMATE USE CASE

Inverse photonics design for illustration purpose.

uniec

#### **INTRA-CELL ROUTING FOR 2-TO-I MULTIPLEXER**

- Shorter path Potential Resistivity (performance) benefit

- Reduction in number of layers Manufacturability & cost benefit

ımec

PUBLIC

Steve Teig, Amazon's VP and Distinguished Engineer, designer of Perceive low-power AI chip, says:

#### **Curvy** is a transformative P&R technology

Simultaneously achieve the following benefits:

| Goal    | Performance          | Total Power  |                    | Area                 | Wirelength | Vias    | Perf / W |

|---------|----------------------|--------------|--------------------|----------------------|------------|---------|----------|

| Balance | +25%                 | -20-25%      |                    | -10%                 | -30-45%    | -40-50% | +50-60%  |

|         | +30-35% for chiplets | -15% dynamic | -25-30%<br>leakage | -20-25% for chiplets |            |         |          |

• Individually achieve the following benefits:

| Goal               | Performance | Total Power | Area    | Perf / W |

|--------------------|-------------|-------------|---------|----------|

| Max Performance    | +40-43%     | +10-15%     | -5-7%   | +25-30%  |

| Max Power Savings  | 0%          | -40-45%     | -8-10%  | +40-45%  |

| Max Area Reduction | +15-18%     | -15-20%     | -10-14% | +35-40%  |

| Max Efficiency     | +20-25%     | -25-30%     | -8-10%  | +65-75%  |

• Improved yield and reliability: 40% fewer vias, lower current density, reduced electromigration

Improved timing closure

© Steve Teig 2025

#### **Get What You Ask For**

By asking for manufacturable shapes,

It will be manufactured as you litho simulated/extracted,

and more reliably

## The BACUS Community Enables All This!

**Questions?**